Verifying stack design with

Speedstack 2008

Application Note

AP511

Why verify stack validity?

A common challenge for PCB designers is verifying that the stack to be sent to a PC fabrication company is manufacturable. With both designer and fabricator able to share Speedstack 2008's builds the PCB designer can forward a proposed stack design to a fabricator to verify that the stack can be built with the fabricator's available materials. The fabricator can utilise Speedstack 2008's "Remake Stack with Autostack" facility to take the stack design and realise it with actual materials automatically.

Speedstack 2008 Si

Speedstack 2008 Stackup Design Systems simplify stack creation and documentation and information sharing for both PCB designer and fabricator. Speedstack 2008 Si is tailored especially for design engineers working with stackups prior to and during layout. Speedstack's documentation includes the stackup design and controlled impedance specifications and test requirements for each layer and enables designers and fabricators to work together to select the best material combinations to minimise build costs.

Remaking the stack with AutoStack

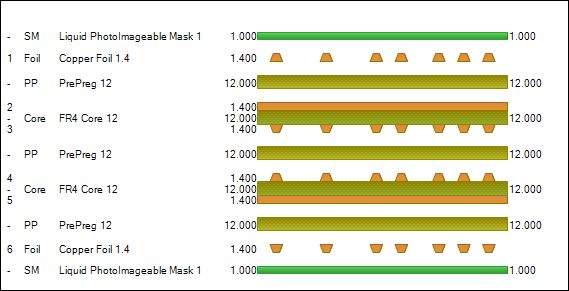

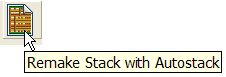

Speedstack 2008 can convert a "generic" stack into a stack with full material specifications with just a few mouse clicks. The graphic above illustrates the Speedstack design documentation for a stack with all its required dimensions, but without actual materials specified. To verify the stack with the PCB fabricator the designer will send the Speedstack documentation to the fabricator. The fabricator will load the stack design into the Speedstack Stack Editor and simply click the Remake Stack with AutoStack button.

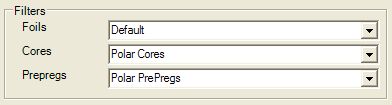

With the appropriate material library loaded and filters applied the fabricator chooses the Cores and Prepregs from the drop down filter lists:

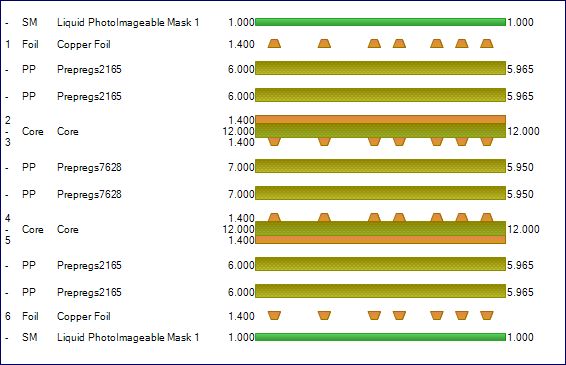

and clicks the Generate Stacks button to build the stack using his available materials. Speedstack regenerates the stack, replacing the designed dimensions with the physical dimensions including the finished thicknesses. The reprocessed stack is shown below.

The resulting stack is sent back to the designer for approval, modification or redesign (for example, it may be necessary to alter trace widths to meet controlled impedance specifications for the available prepreg or core thicknesses.)

What

if you continue to use informal methods for stackup

validation?

By using informal methods for validating your

stackup, or not validating at all, you risk specifying a

stackup where, for example, the controlled impedance

values are not optimised or are slightly out of

specification, or worse, a stack that cannot be built,

(where controlled impedance values cannot be realised

with the proposed dimensions or a board made too thick

for an edge connector).

Working with Speedstack's Remake facility

Taking advantage of Speedstack's Remake facility greatly increases your confidence of a successful build on the first pass and improves communication between designer and fabricator. Correcting the stack at this stage produces a fully documented stack and can save very costly and time consuming mistakes later.

To learn more about Speedstack 2008 please contact one of the Polar representatives below: