# Coated Microstrip 1B Edge-Coupled Offset Striplines 2BIAIR Surface Coplanar Strips With Ground 2B Coated Coplanar Strips 2B Diff Coated Coplanar Waveguide 2B Diff Coated Coplanar Wavegui

### Speedstack 2021 - 2023 Updates

Richard Attrill – June 2023 (Rev 12)

### Speedstack v23.06.15 (June 2023)

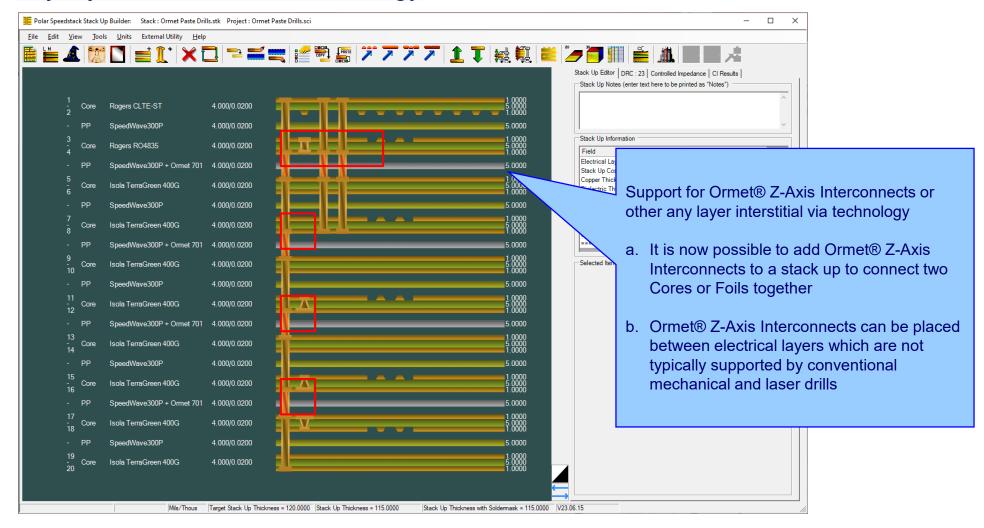

## <u>Drill Enhancements including support for Ormet® Z-Axis Interconnects or other any layer interstitial via technology</u>

## <u>Drill Enhancements including support for Ormet® Z-Axis Interconnects or other any layer interstitial via technology</u>

| Configuration Options                                                                                                                                                                                                                                                                                                              | ×                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| External Utilities   Rebuild and Calculate Structures   General   Structure Defaults   Licensing   File Locations   Goal Seeking   User   CITS Test   Colours   Miscellaneous   Hatch                                                                                                                                              | Defaults                                                                                                                               |

| Number of Undo Levels  Maximum Laser Drilled Layers  5                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| ☐ Drill Validation Check                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

| This option prevents invalid drills from being added to the stack up. For instance, a drill that starts from the lower copper sid materials. Uncheck this option if you use a drilling technology that permits drills to be placed between electrical layers which typically supported by conventional mechanical and laser drills | e of core<br>h are not                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                    | Support for Ormet® Z-Axis Interconnects or other any layer interstitial via technology (continued)                                     |

| Apply                                                                                                                                                                                                                                                                                                                              | A new Tools   Options   Miscellaneous tab Drill Validation Check option has been introduced.                                           |

|                                                                                                                                                                                                                                                                                                                                    | Unchecking this option will disable the Speedstack invalid drills check in order to support the Ormet® Z-Axis Interconnects technology |

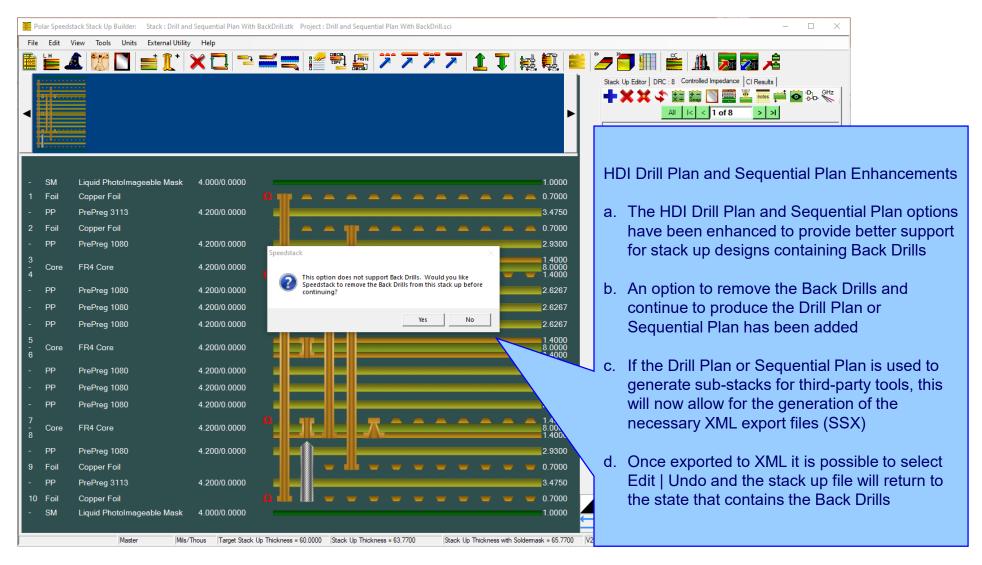

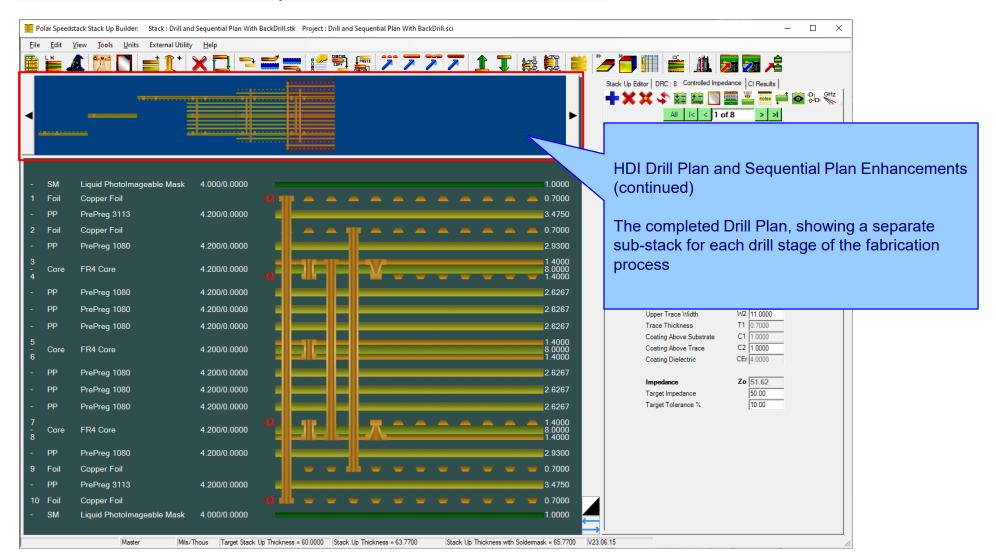

#### HDI Drill Plan and Sequential Plan Enhancements

#### HDI Drill Plan and Sequential Plan Enhancements

### Speedstack v23.05.01 (May 2023)

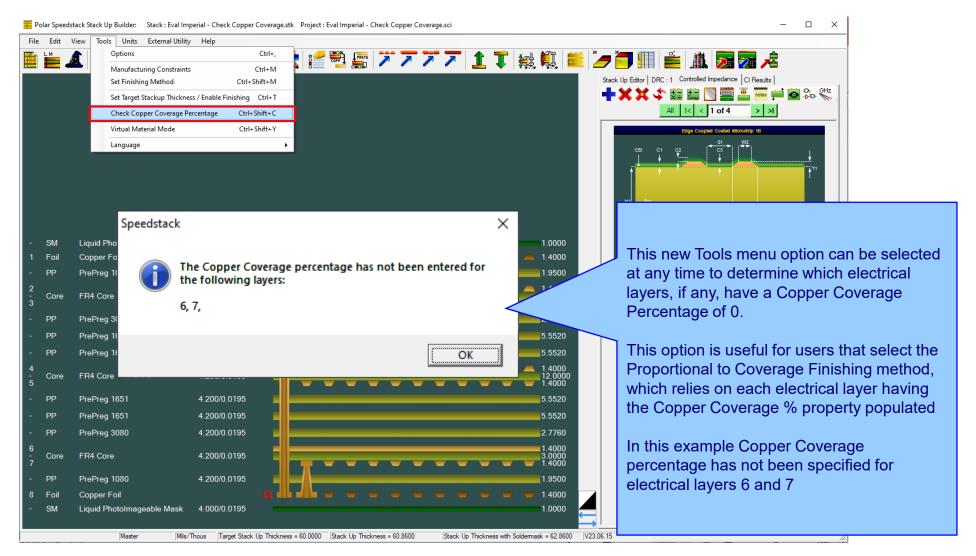

#### New Check Copper Coverage Percentage option

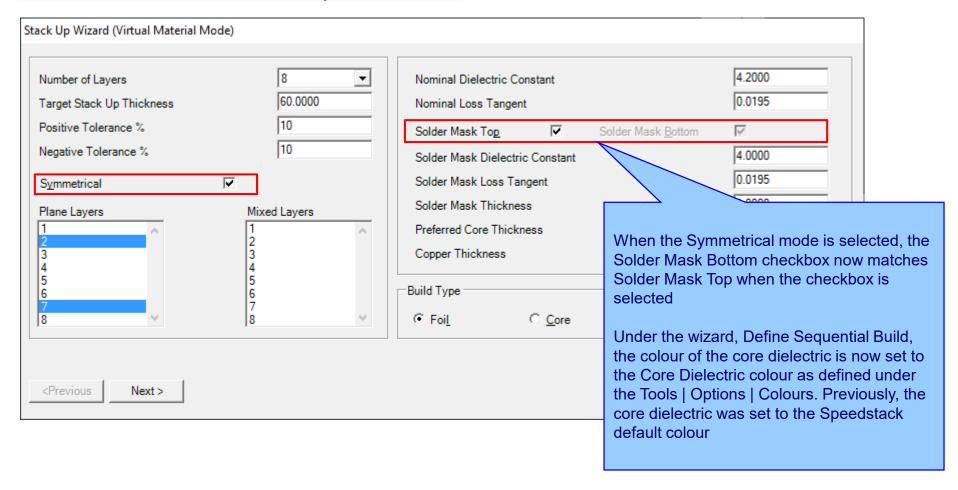

#### <u>Virtual Material Wizard Improvements</u>

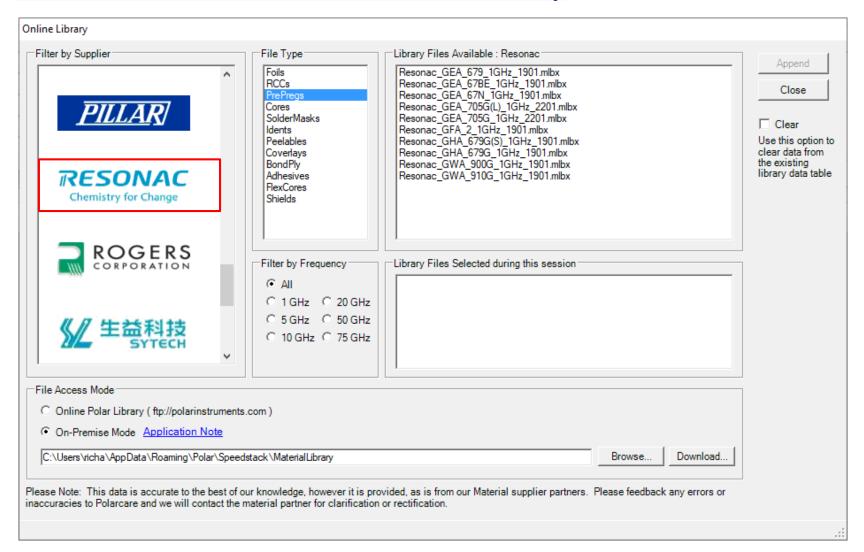

#### Resonac materials added to the Online Library

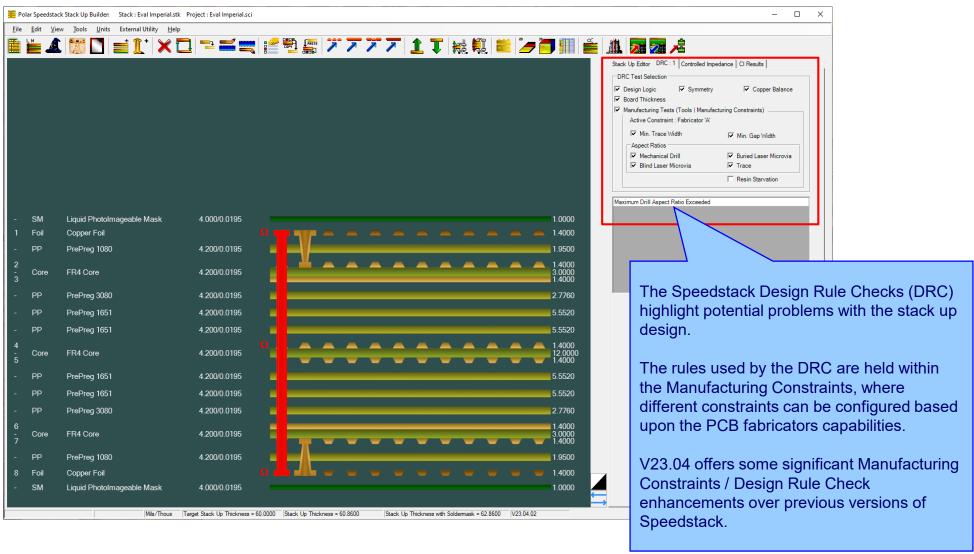

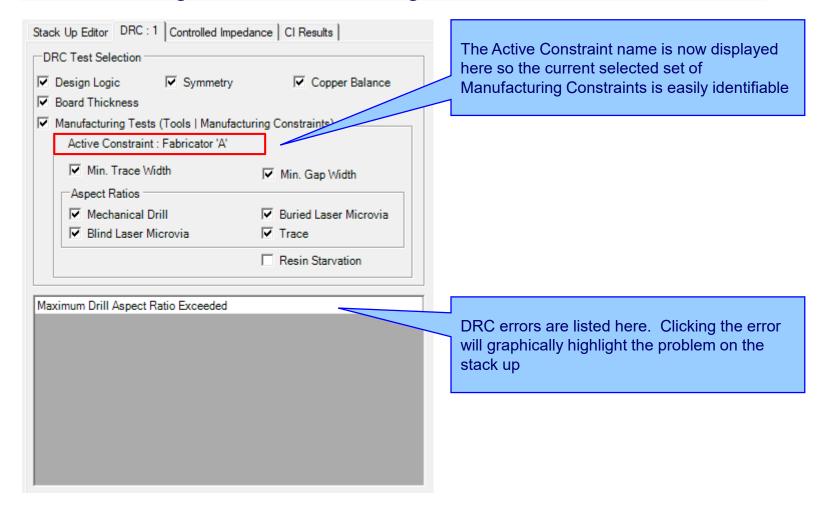

### Speedstack v23.04.02 (April 2023)

### Speedstack v23.03.01 (March 2023)

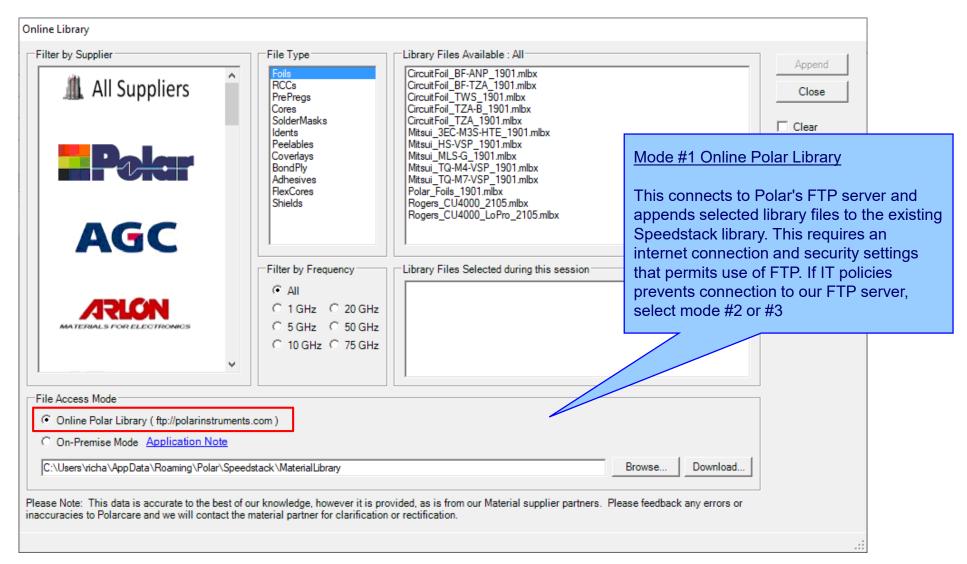

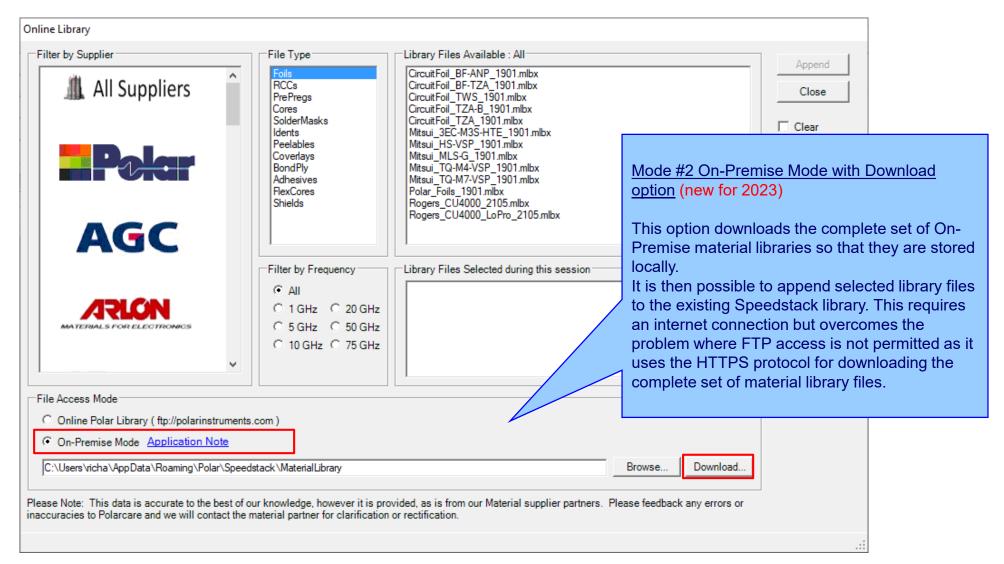

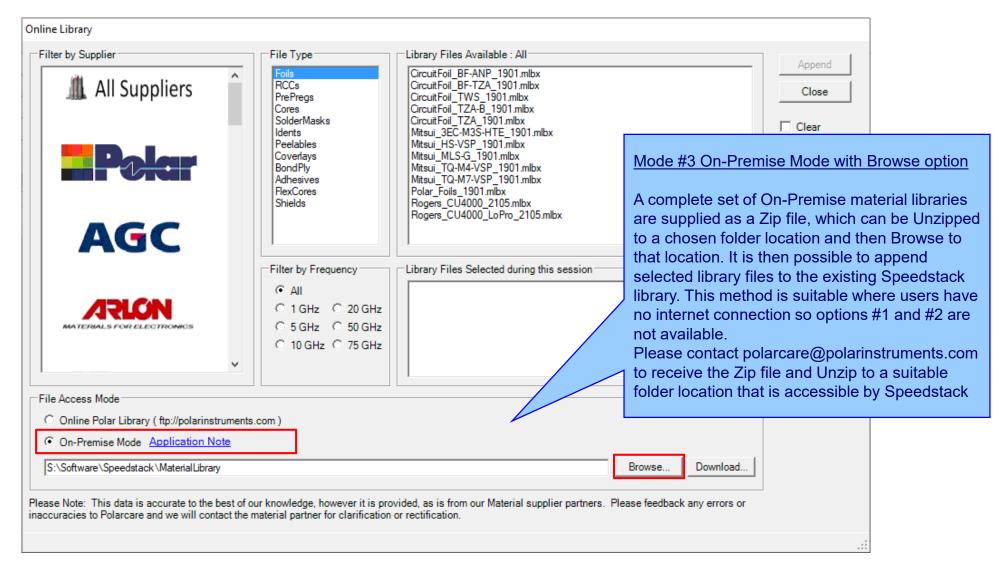

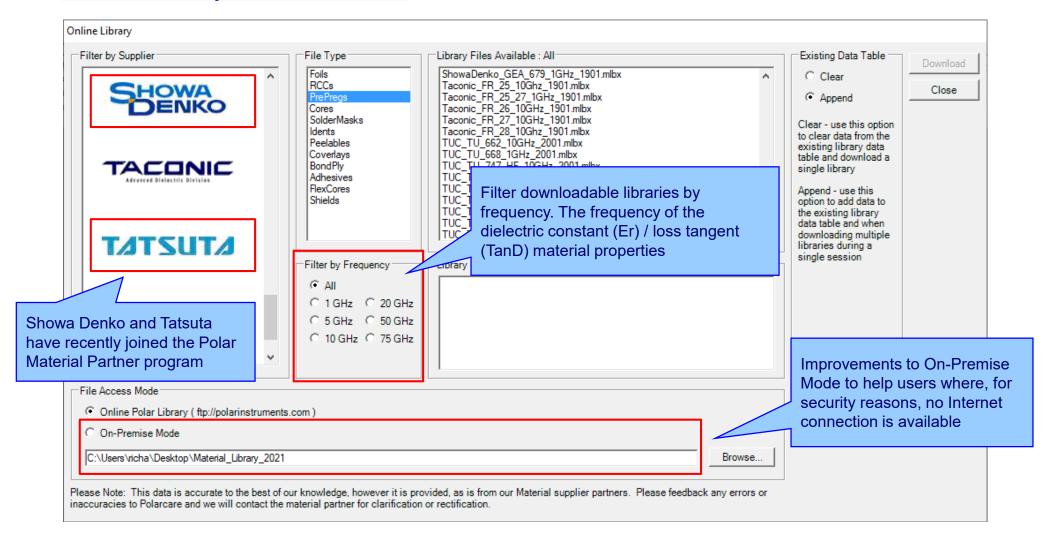

#### Online Library – Now supports three modes

#### Online Library - Now supports three modes

#### Online Library - Now supports three modes

### Speedstack v22.11.01 (November 2022)

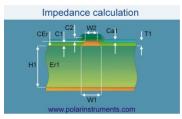

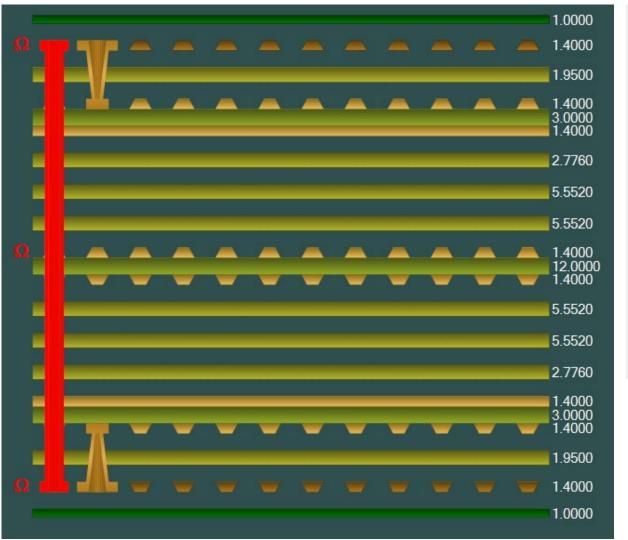

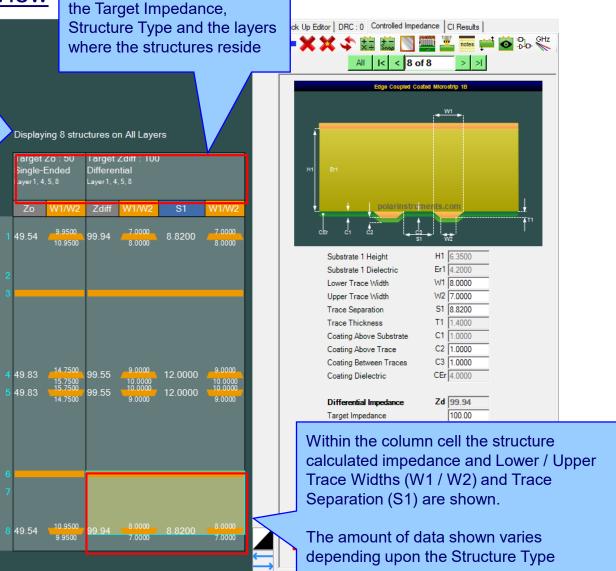

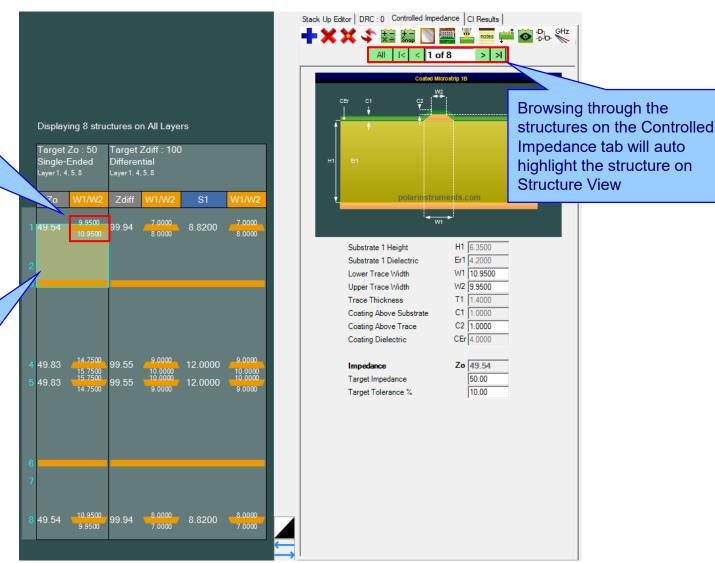

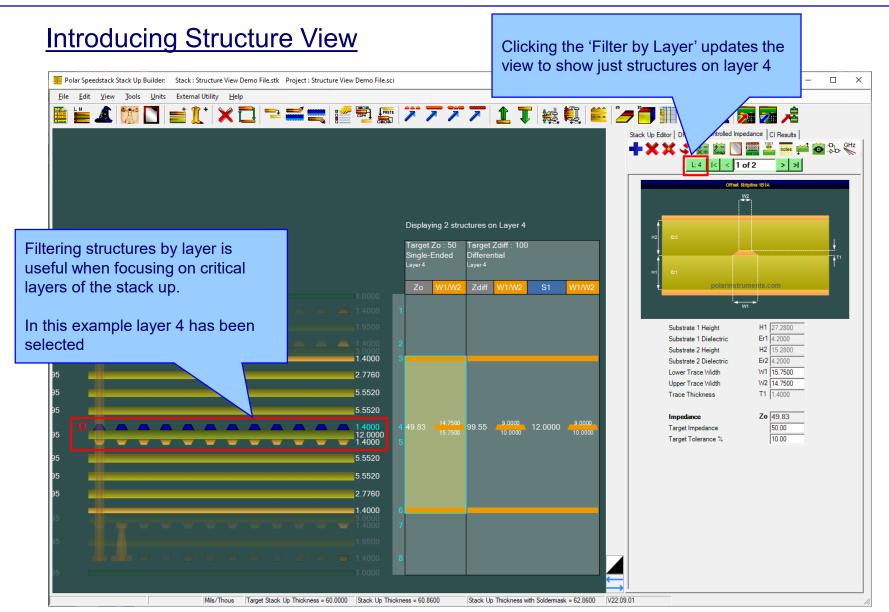

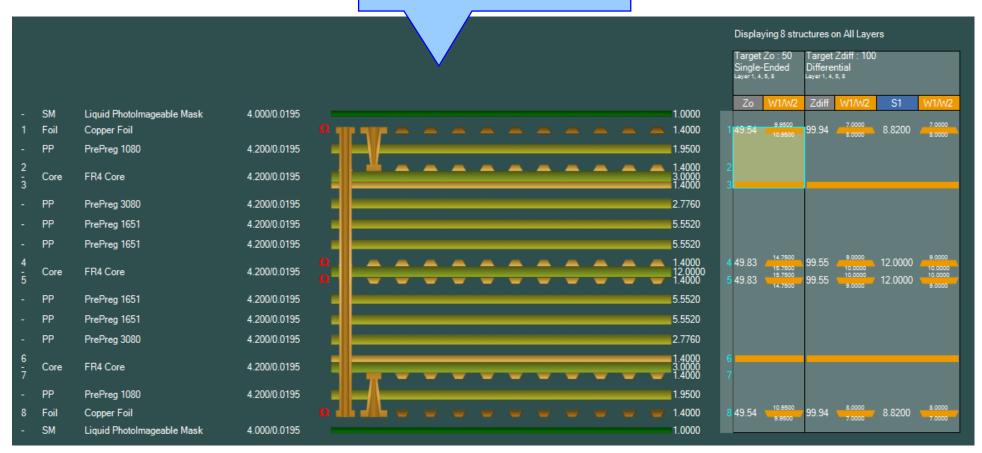

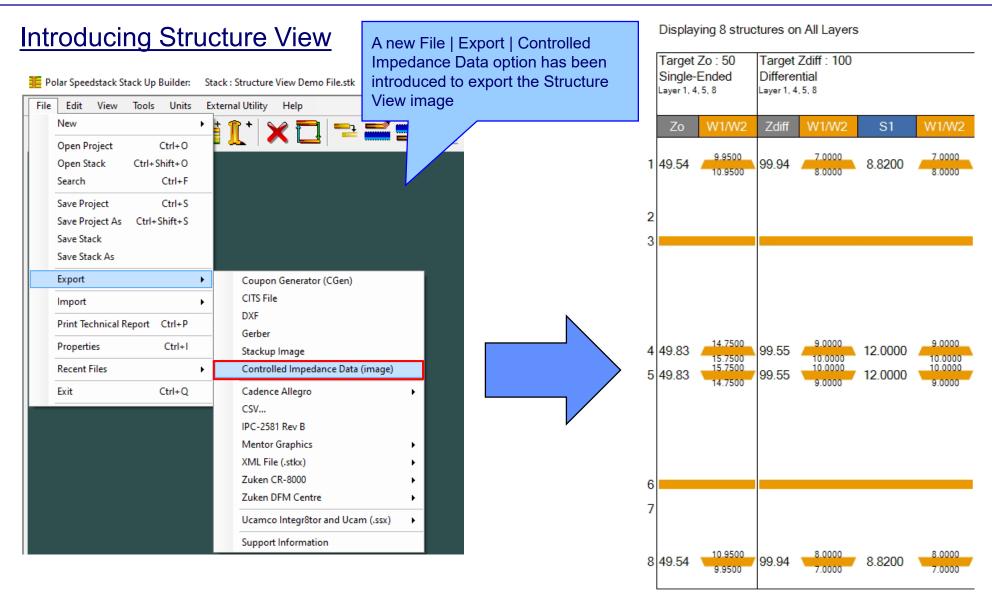

#### Introducing Structure View Structure View presents a useful overview of the controlled impedance / insertion loss structures that exist on the stack up Folar Speedstack Stack Up Builder: Stack: Structure View Demo File.stk Project: Structure View Demo File.sci File Edit View Tools Units External Utility Help | 🖸 | 🚅 🛴 | 🗶 🚍 | 🎏 🏣 | ア ア ア ア 👤 📵 🙀 💜 All | |< | 1 of 8 Displaying 8 structures on All Layers 1.9500 Substrate 1 Dielectric 1.4000 3.0000 1.4000 Upper Trace Width 2.7760 Coating Above Substrate 5.5520 Coating Above Trace Coating Dielectric 5.5520 1.4000 12.0000 1.4000 Zo 49.54 50.00 Target Tolerance % 5.5520 5.5520 2.7760 000 The new Structure View is positioned to the To access Structure View simply right of the existing stack up. All structures are 49.54 10.9500 99.94 8.0000 8.8200 drag the stack up to the left or use aligned with the stack up electrical layers on the new Show / Hide Structure which they reside View tool bar button k Up Thickness = 60.8600 Stack Up Thickness with Soldermask = 62.8600

#### **Introducing Structure View**

Structures are arranged by Target Impedance, low to high, then by Structure Type.

All structures of the same

Target Impedance and

Structure Type will be

positioned in the same column

In this example there are 8 structures in total:

4 x 50 ohm singled-ended (column 1)

4 x 100 ohm differential (column 2)

The column header contains

#### **Introducing Structure View**

Structure View is interactive. Clicking on the golden trace will auto-switch to that structure on the Controlled Impedance tab

The transparent blue highlight reflects the current structure selected on the Controlled Impedance tab

#### **Introducing Structure View**

Use the mouse wheel to zoom out and show the complete stack up together with the structures.

All data is now visible in one view

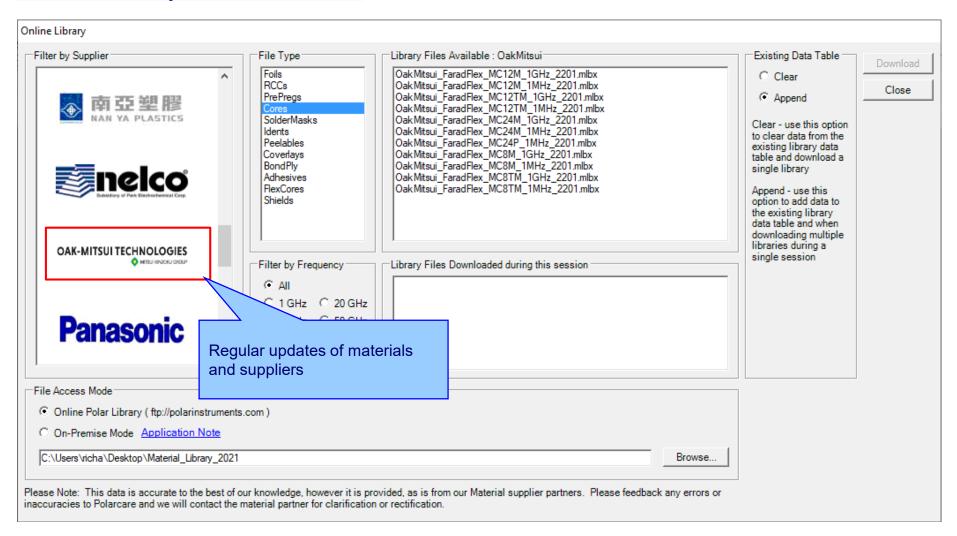

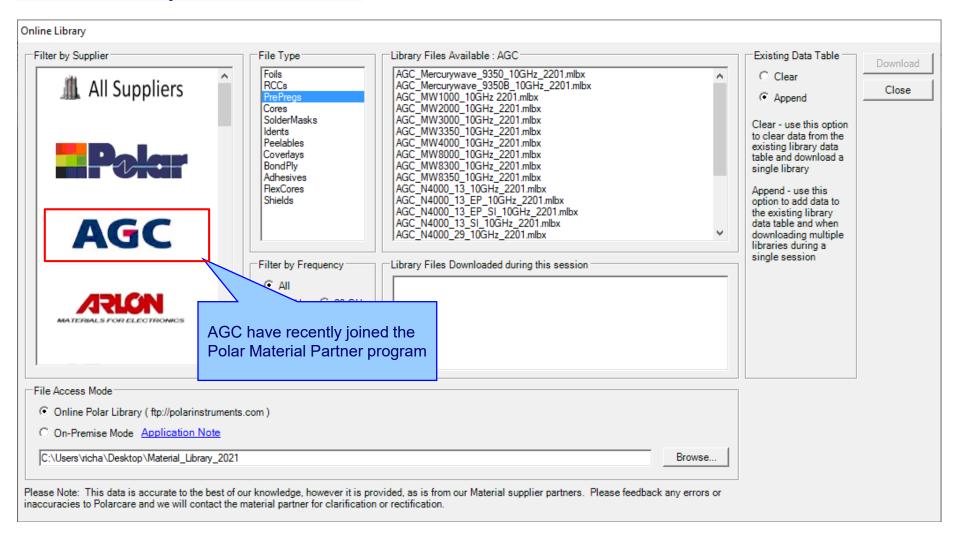

#### Online Library enhancements

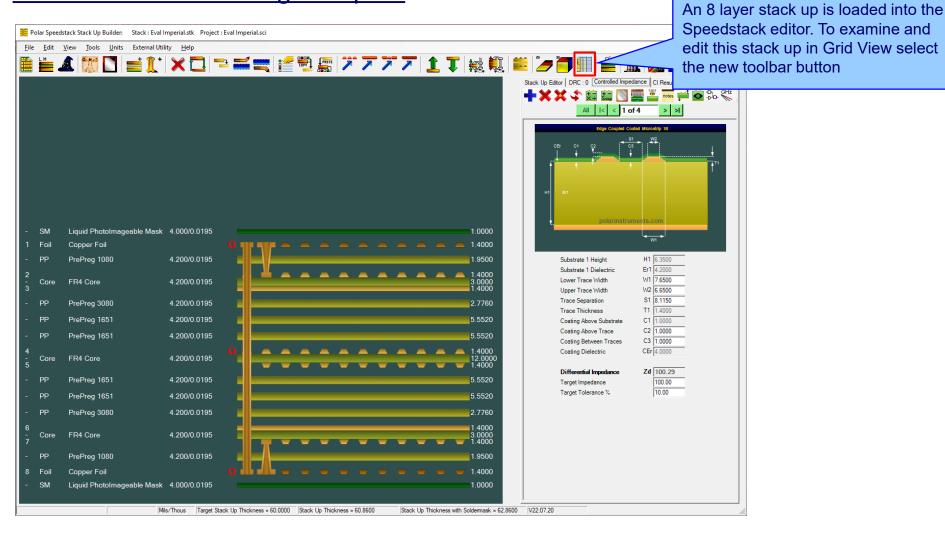

### Speedstack v22.07.20 (July 2022)

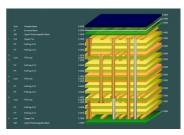

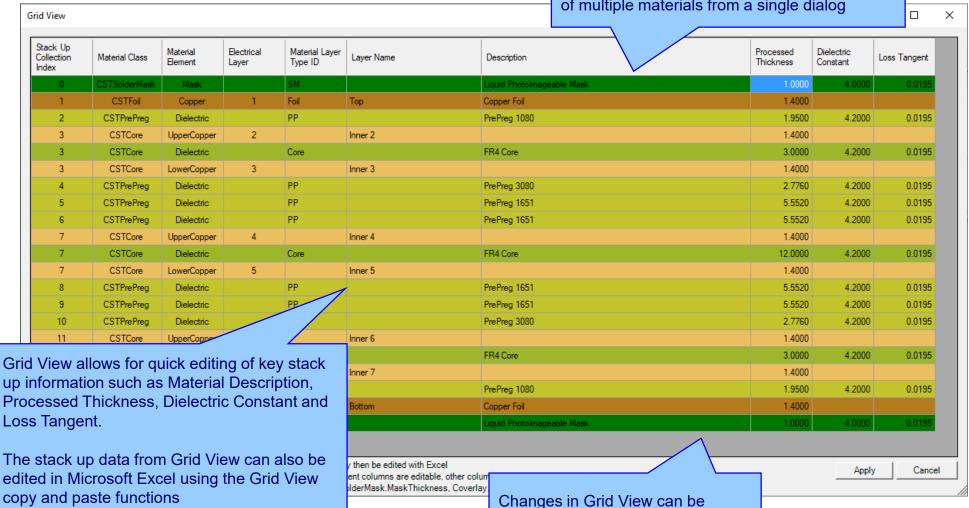

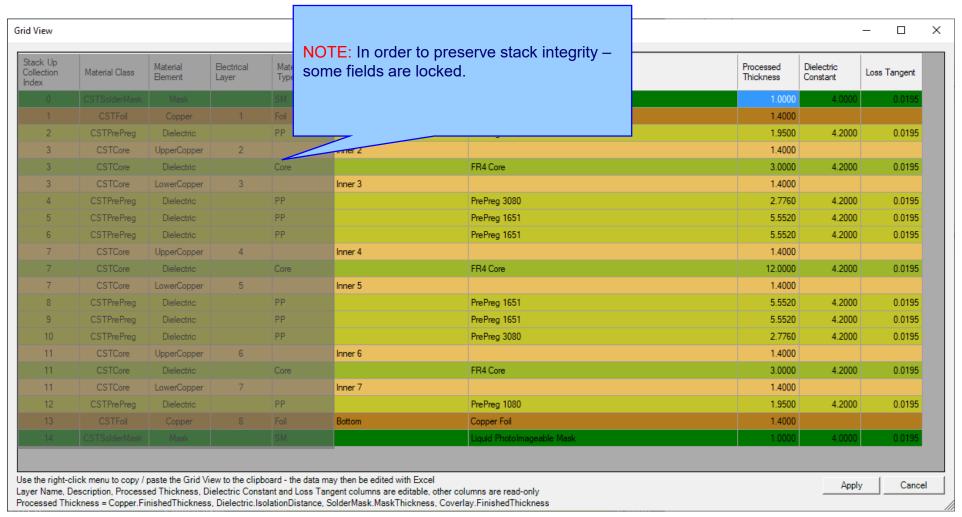

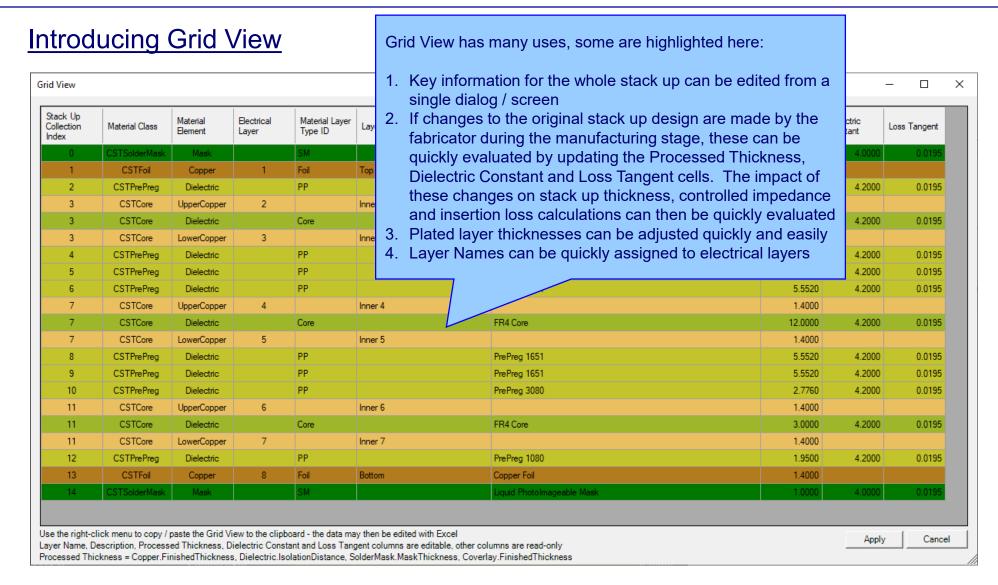

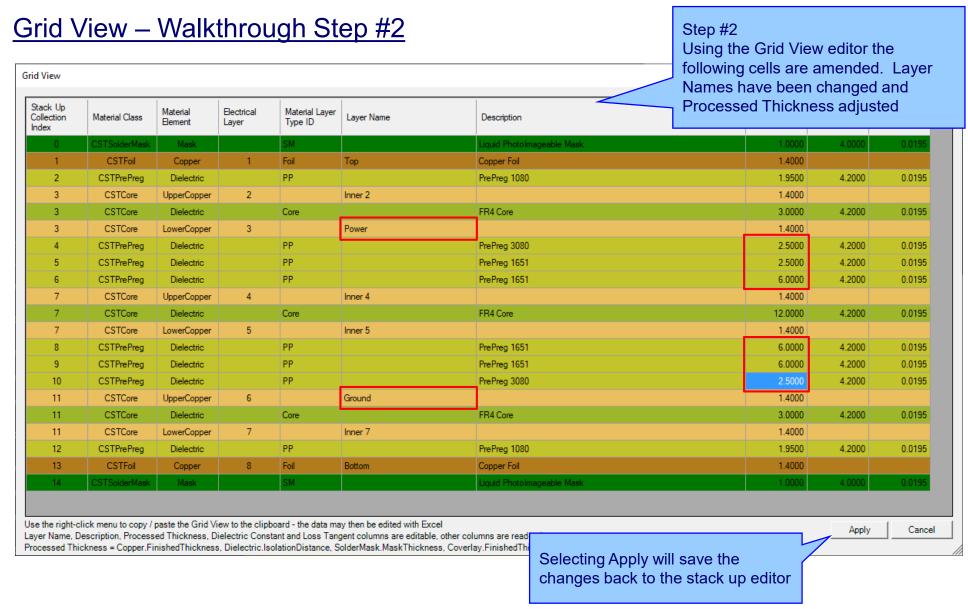

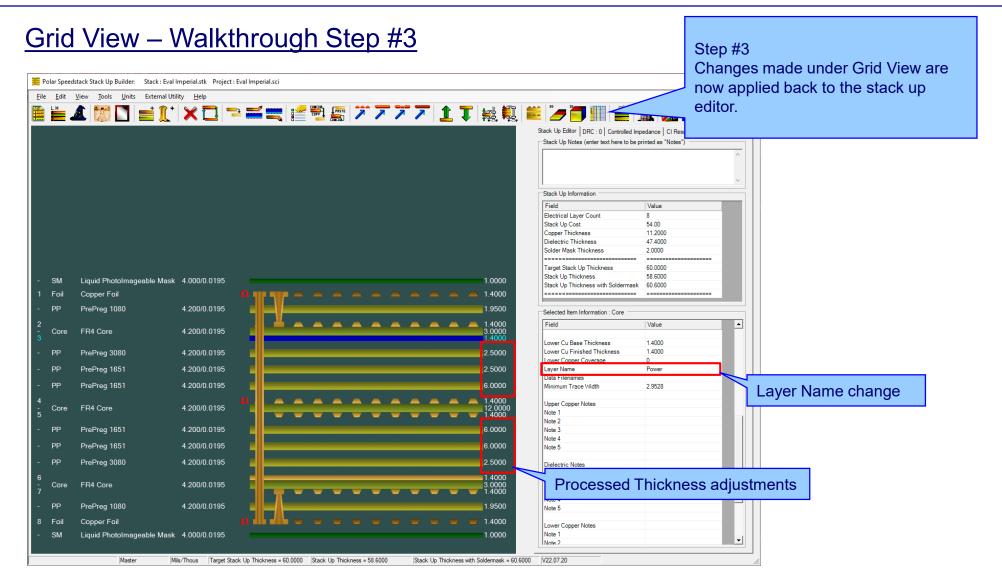

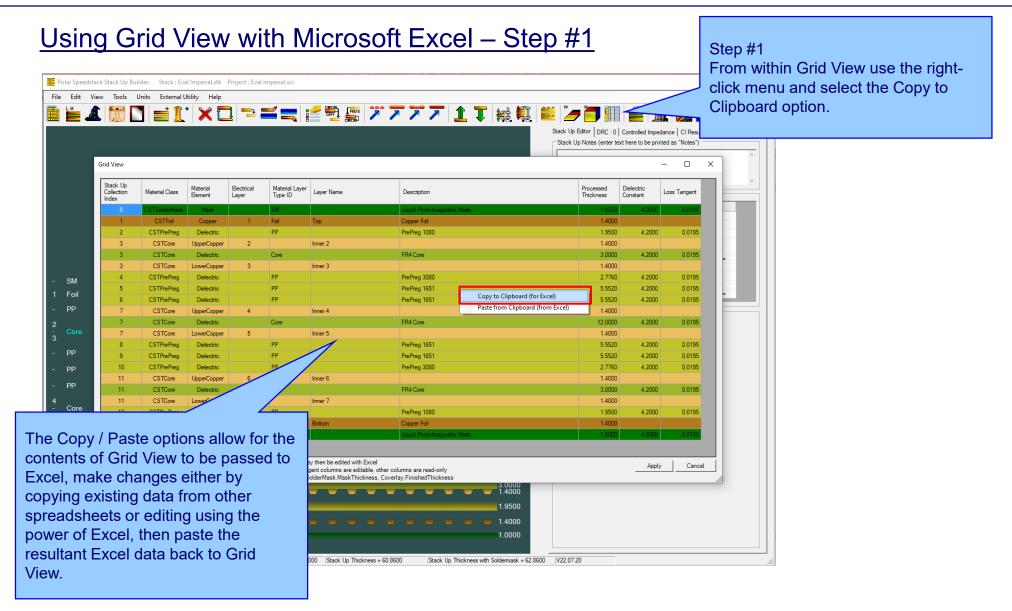

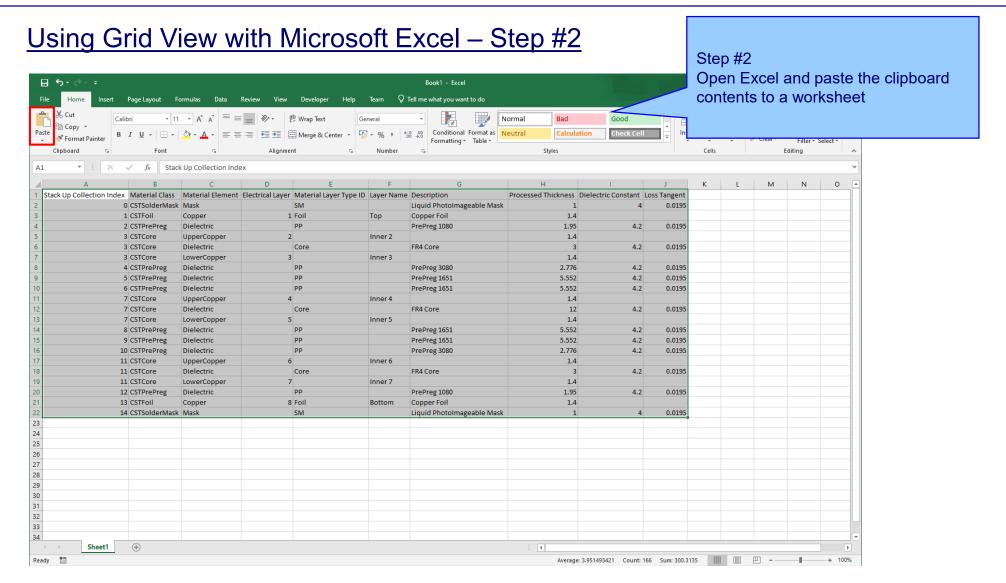

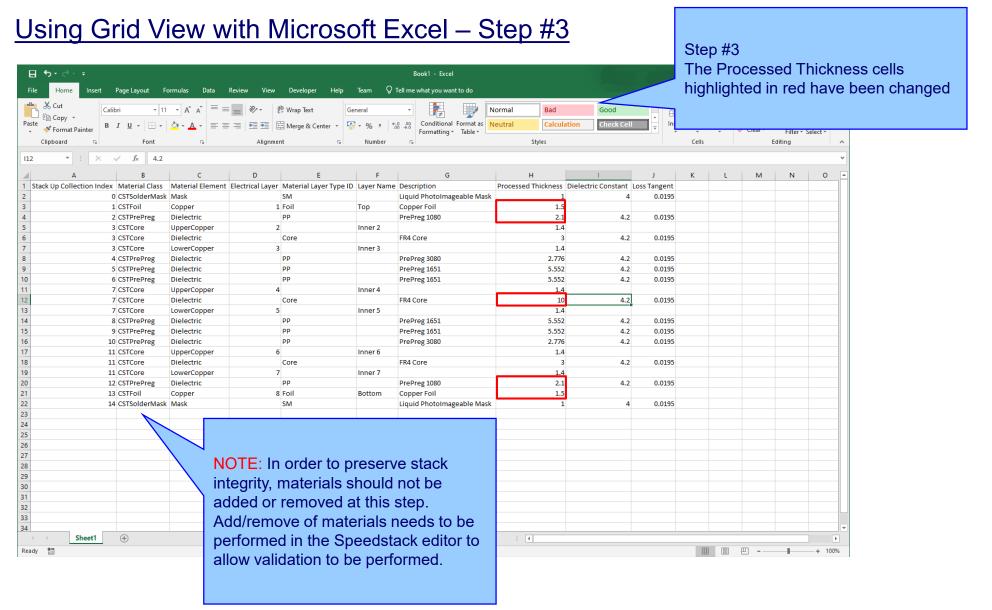

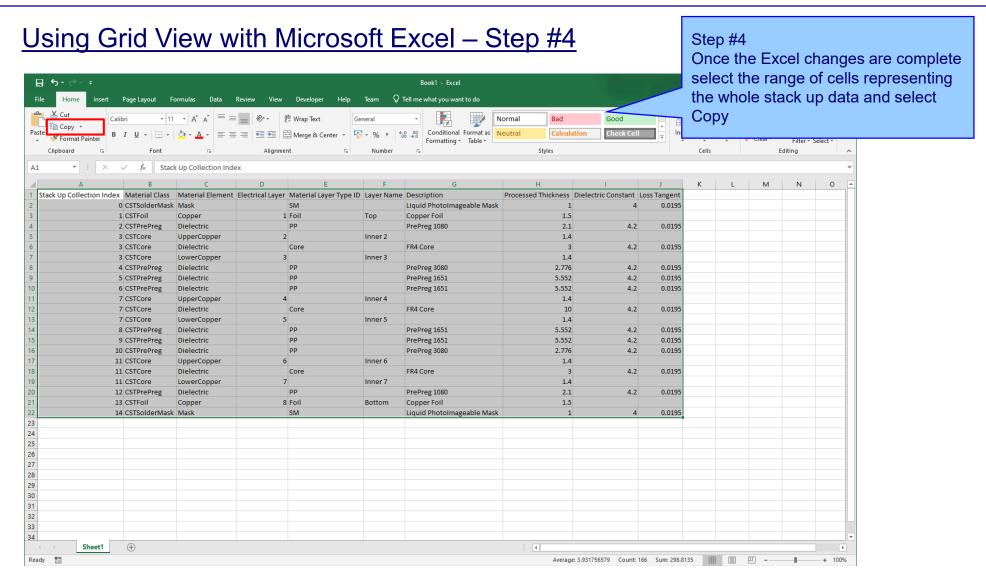

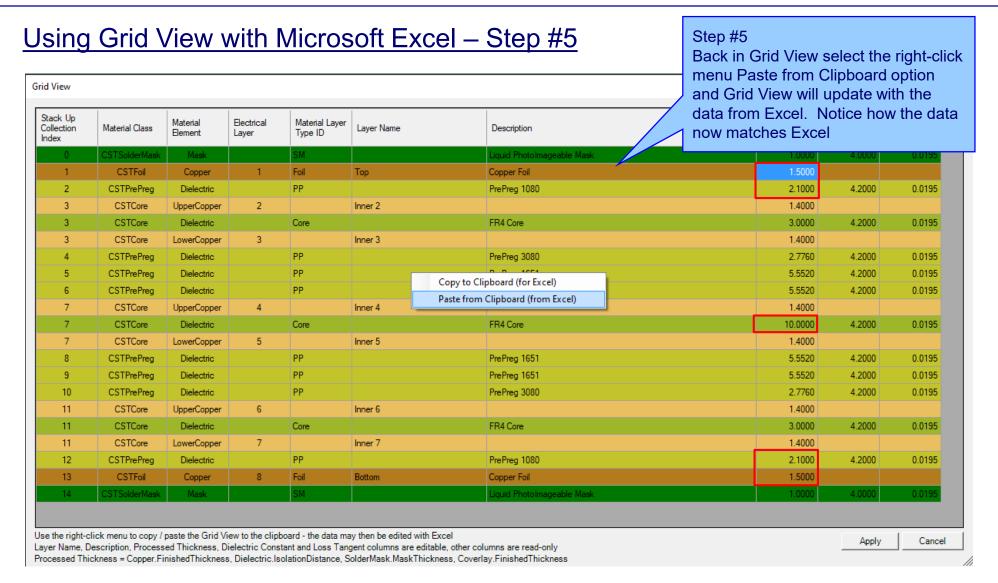

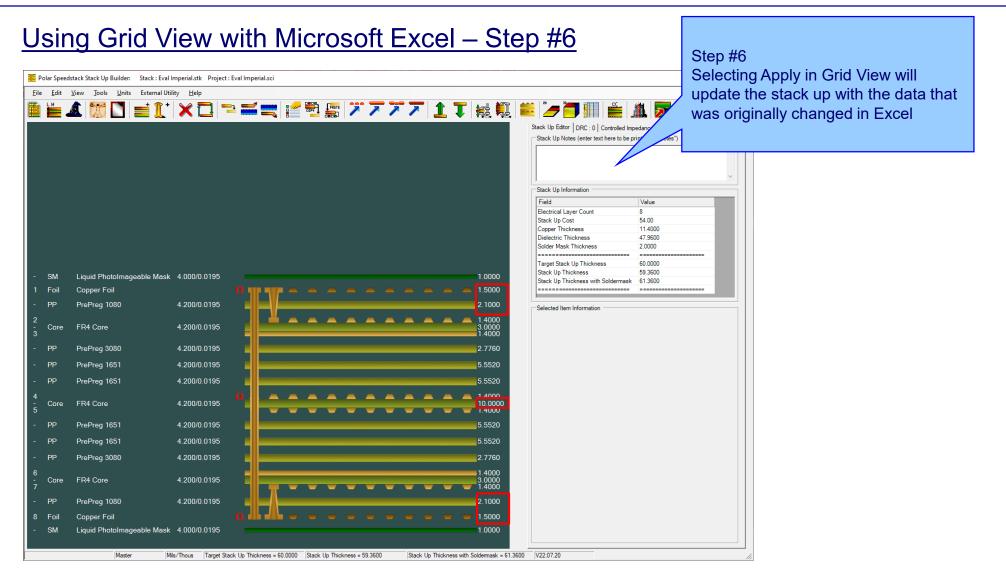

#### **Introducing Grid View**

Grid View presents the current stack up in an editable data grid form to allow for easy editing of multiple materials from a single dialog

design

saved back to the original stack up

#### Introducing Grid View

Step #1

# <u>Grid View – Walkthrough Step #1</u>

#### Other enhancements

- Stack Up Notes user interface improvements

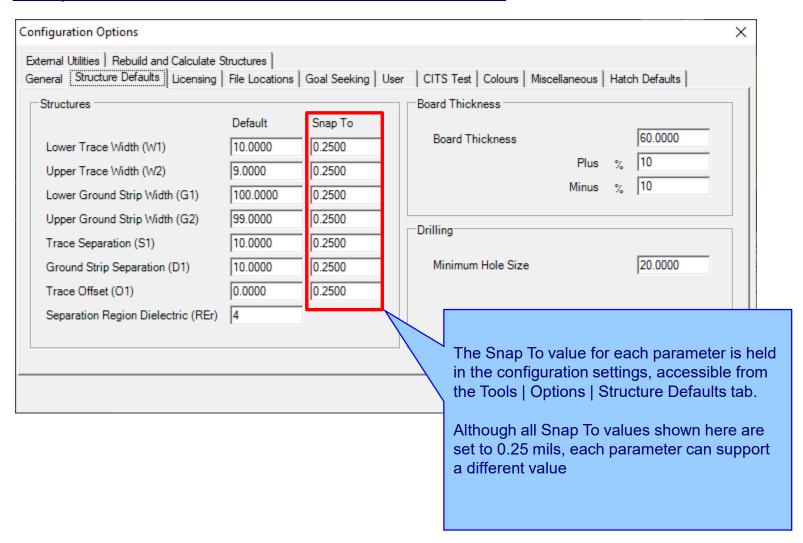

- The Tools | Options | Structure Defaults | Separation Region Dielectric (REr) now supports double data types. Previously, it only supported integers

# Speedstack v22.05.06 (May 2022)

# Online Library enhancements

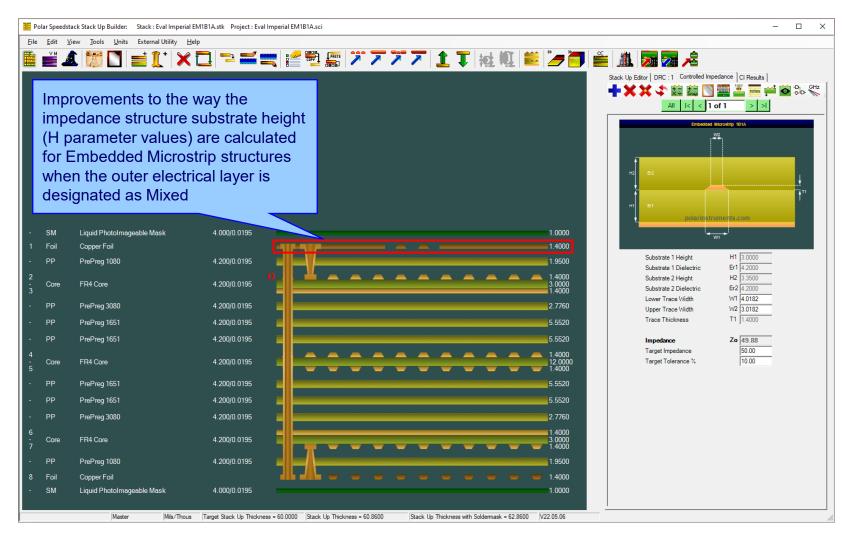

# Embedded Microstrip structure enhancements

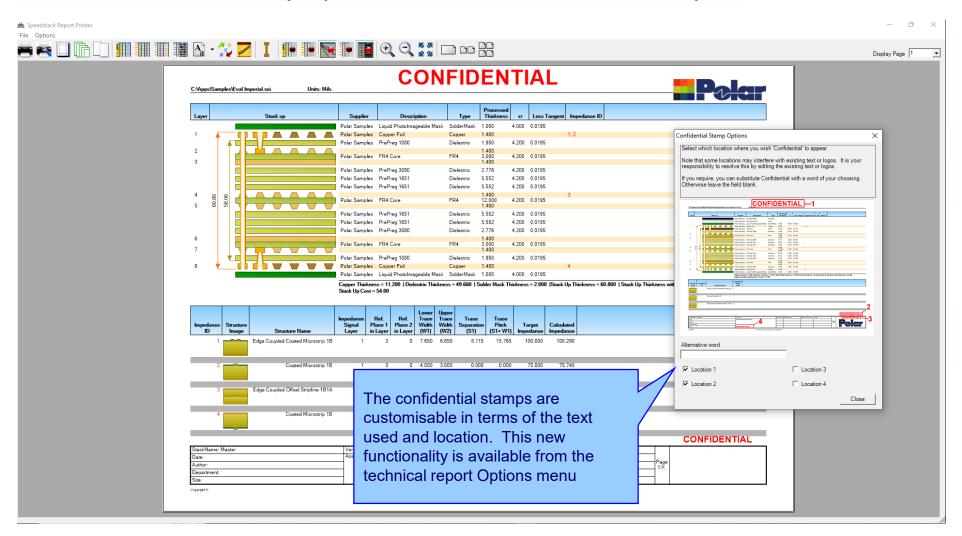

#### New Confidential Stamp options added to the technical report

# Speedstack v22.01.01 (January 2022)

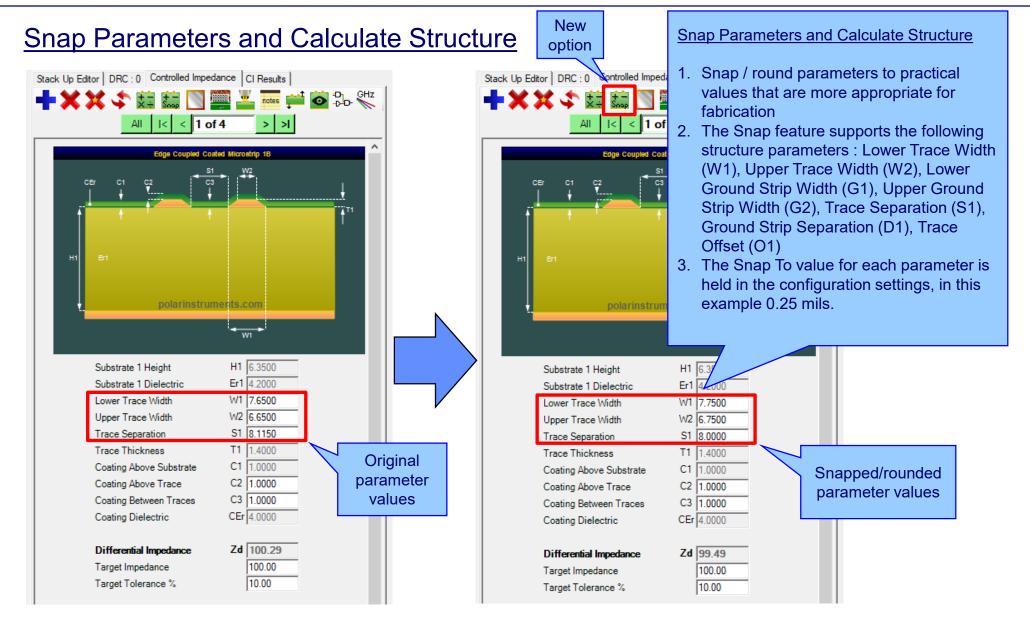

#### **Snap Parameters and Calculate Structure**

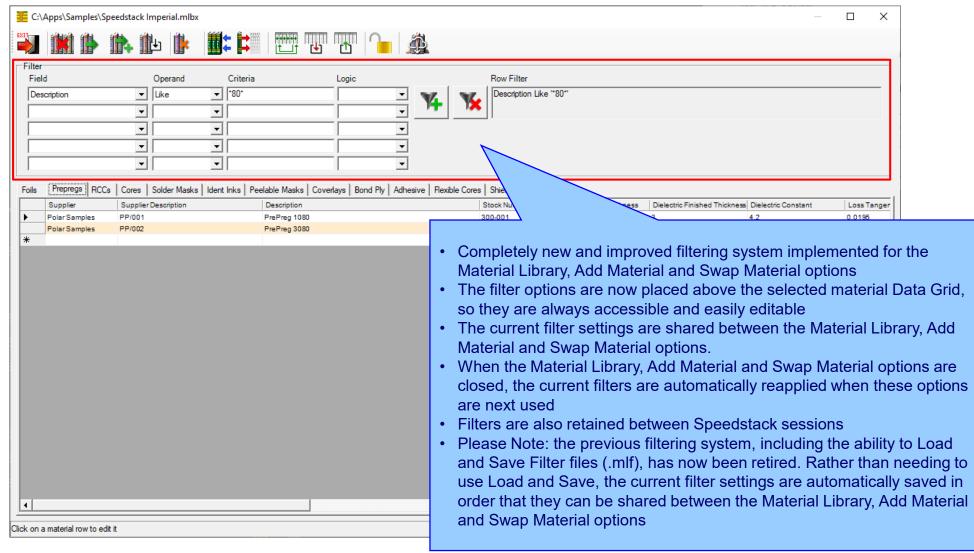

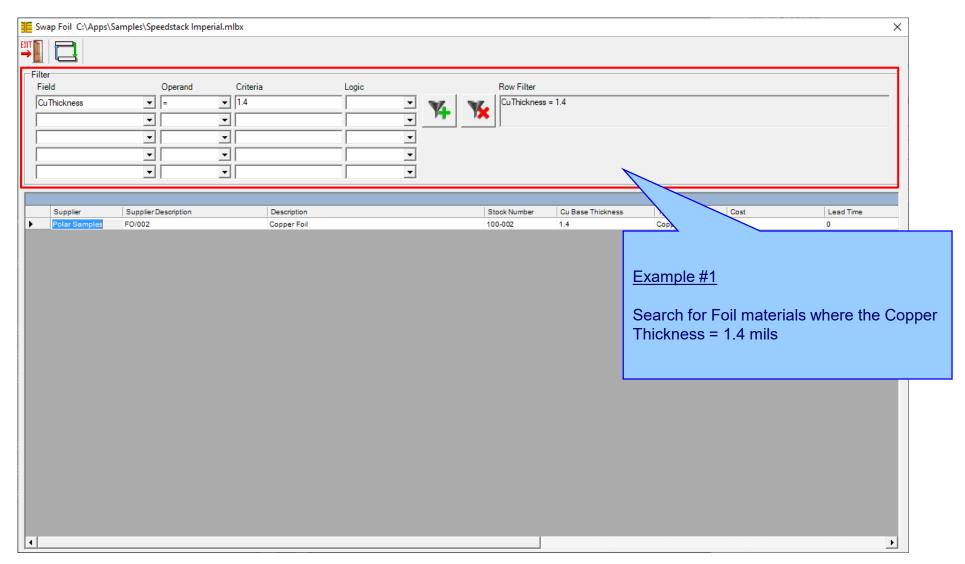

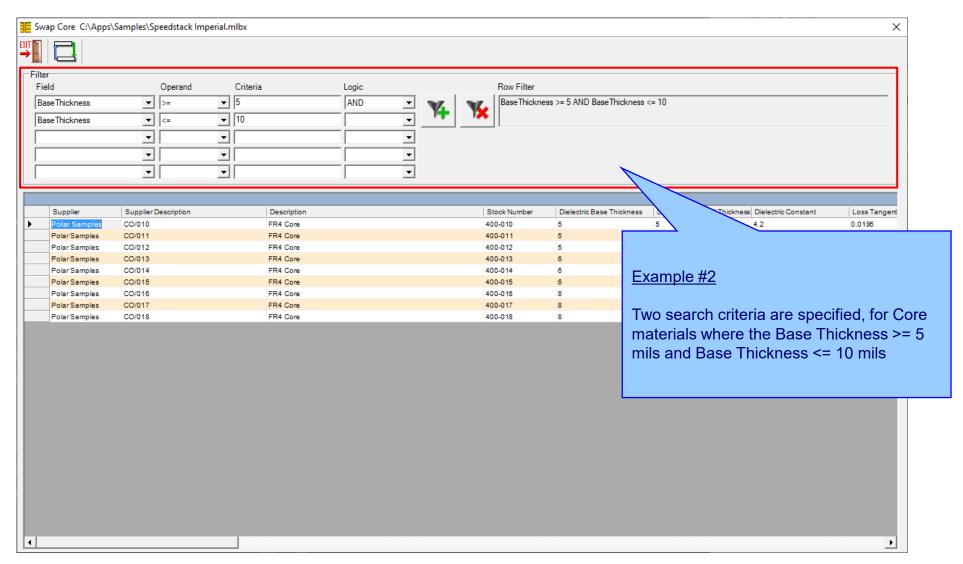

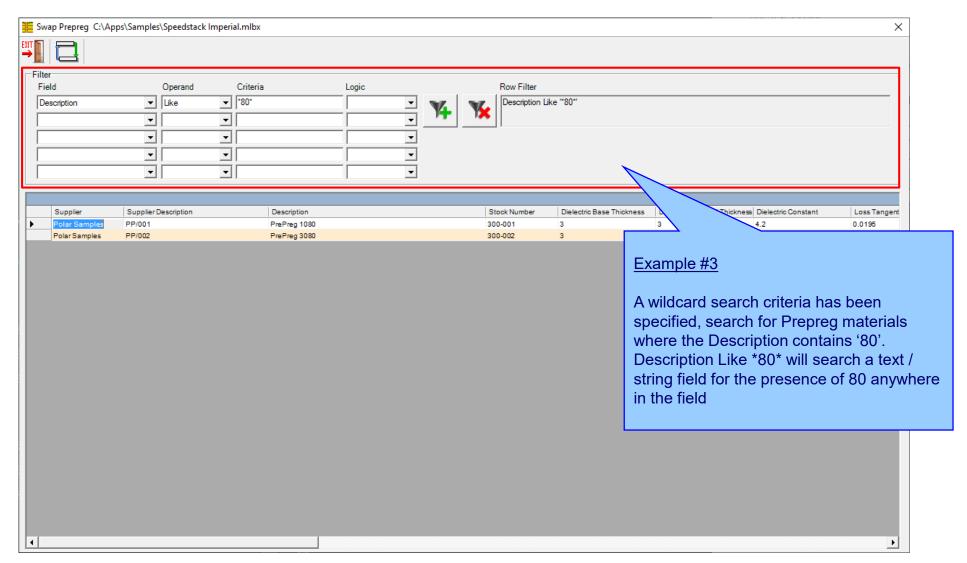

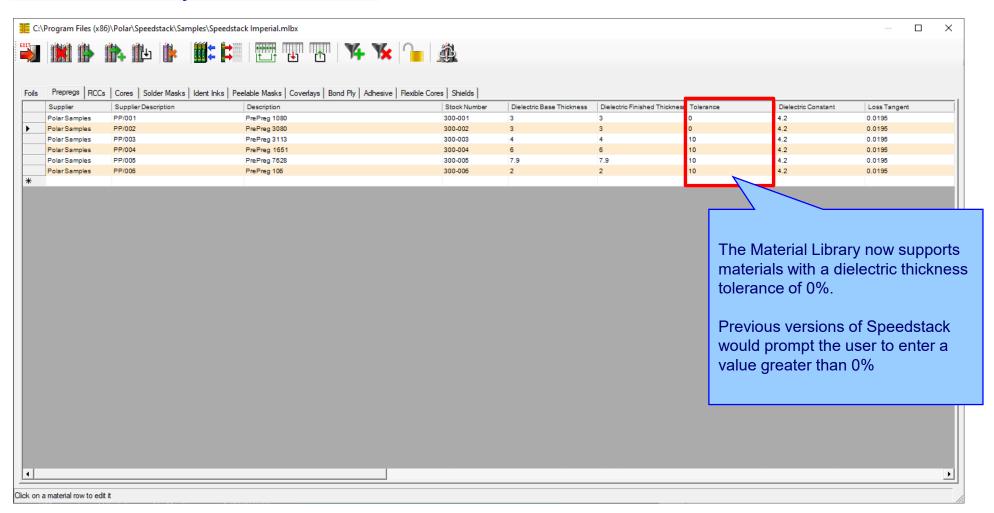

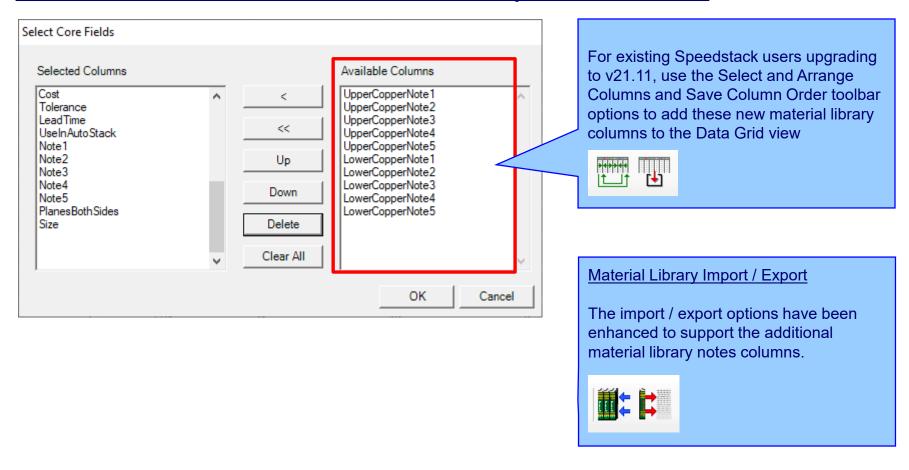

# **Material Library Enhancements**

# Speedstack v21.11.01 (November 2021)

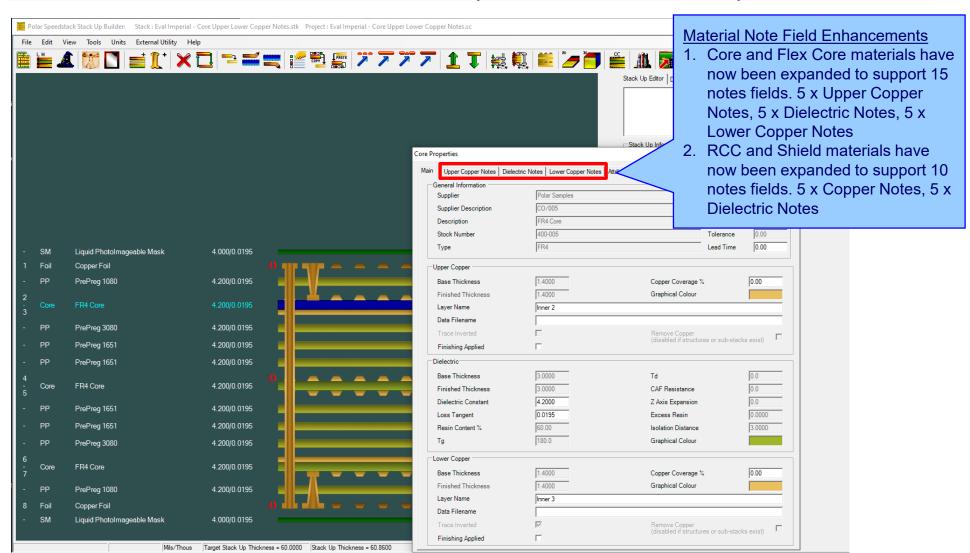

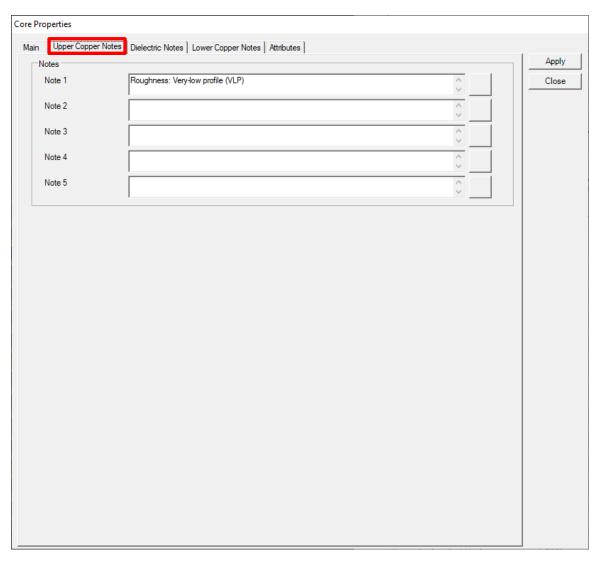

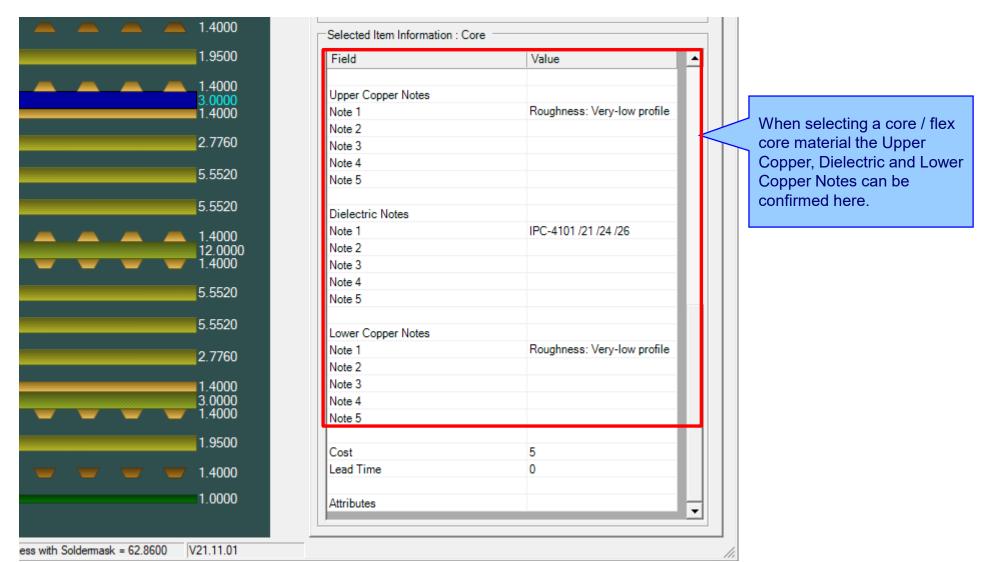

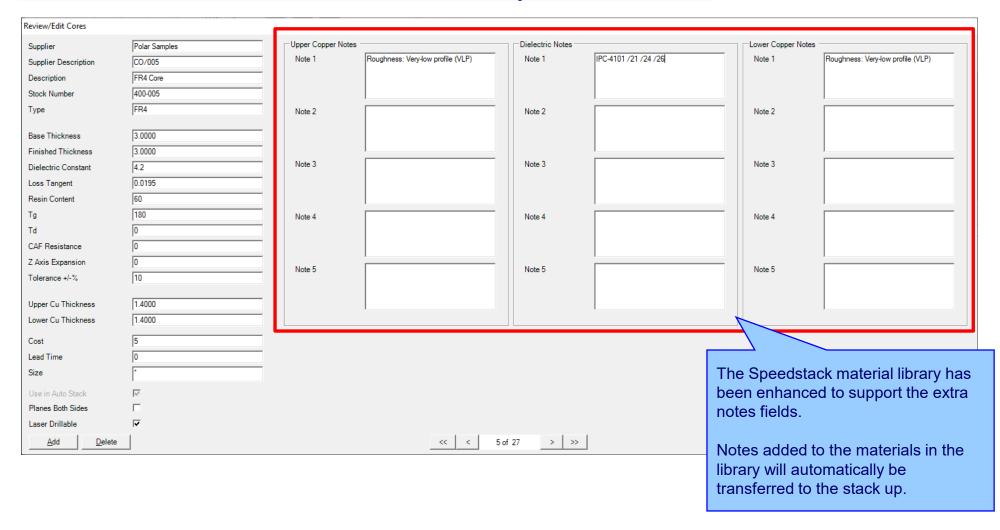

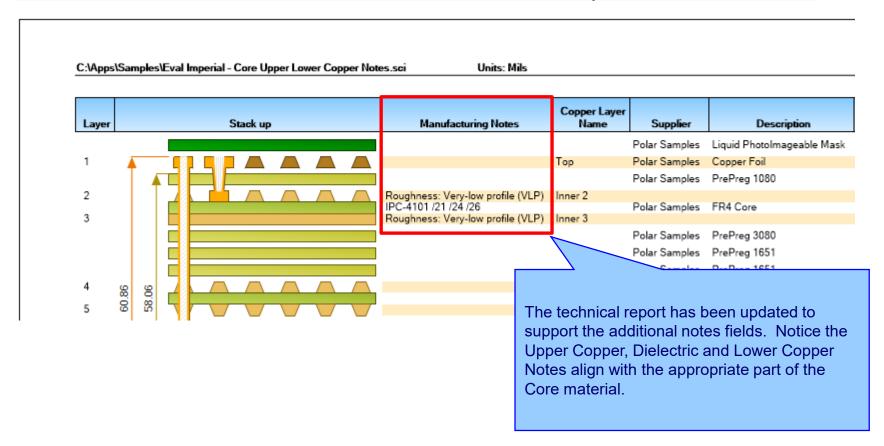

The new Upper and Lower Copper Notes allow the user to specify important information about the copper surfaces for a Core and Flex Core material.

For instance, copper roughness and plating fabrication information can be specified

Dielectric Notes are useful for specifying IPC-4101 slash sheet categories, glass weave information (spread glass) and other important information regarding the dielectric region of the core.

The existing five Notes fields from previous versions of Speedstack will be allocated as Dielectric Notes.

# <u>Material Note Field Enhancements – library enhancements</u>

#### <u>Material Note Field Enhancements – library enhancements</u>

#### <u>Material Note Field Enhancements – technical report enhancements</u>

### <u>Import / Export enhancements</u>

The following Import / Export options have been updated to support the additional material notes properties introduced with Speedstack v21.11.01:

- XML STKX v23.00 and SSX v13.00 import / export options

- CSV export option

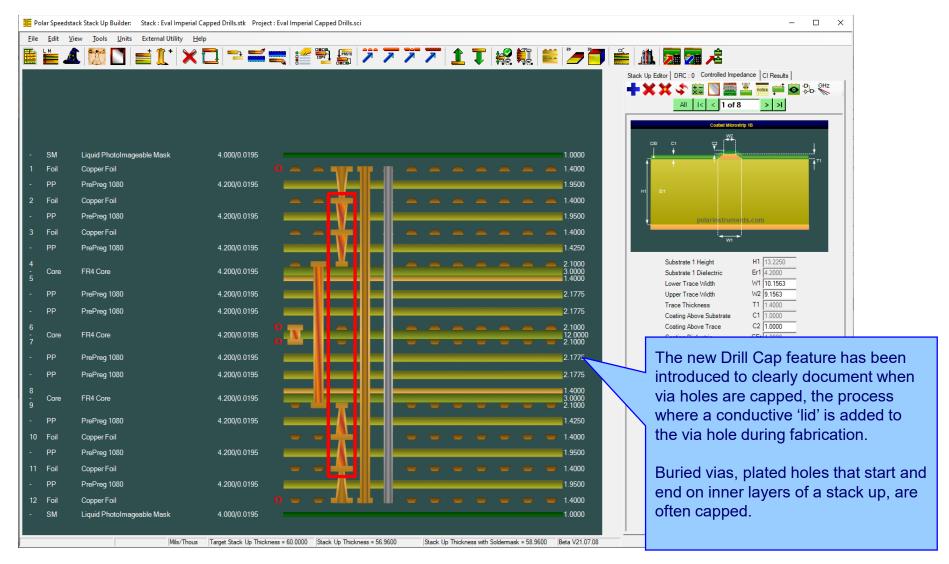

# Speedstack v21.07.08 (July 2021)

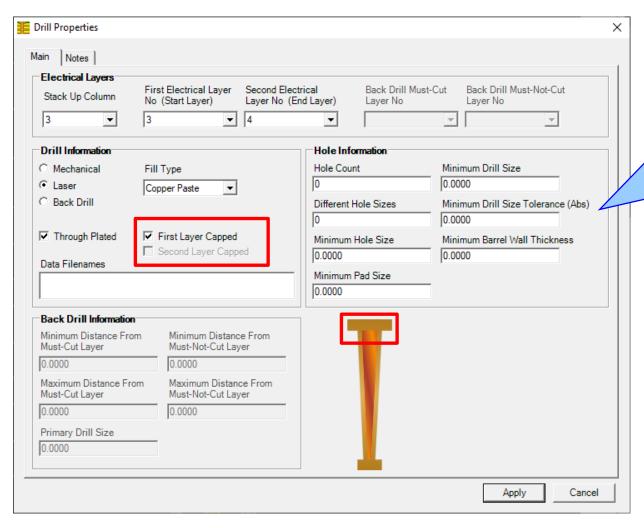

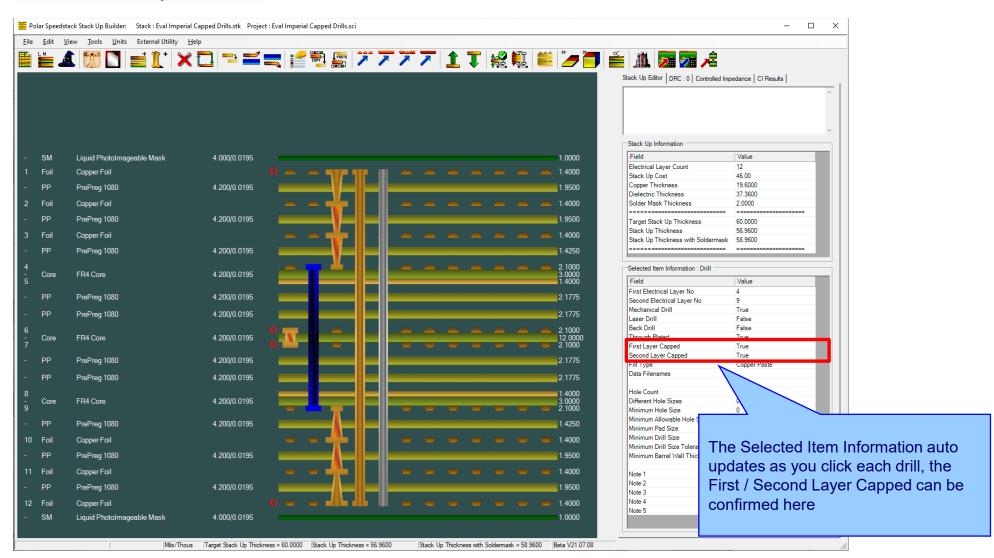

# New Drill Cap feature

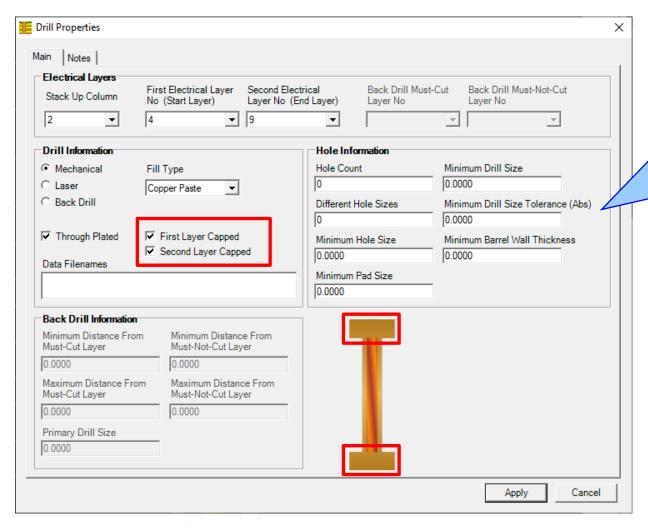

# <u>Drill Cap option – mechanical through plated drills</u>

#### Mechanical

For mechanical drills it is possible to have four states:

- 1.Neither first or second layer capped (default when adding a drill)

- 2.First layer capped

- 3. Second layer capped

- 4.Both layers capped

# <u>Drill Cap option – laser drills</u>

#### Laser

For laser drills it is possible to have two states as the Second Layer Capped checkbox is disabled:

- 1.Not capped (default when adding a drill)

- 2.First layer capped

# New Drill Cap feature

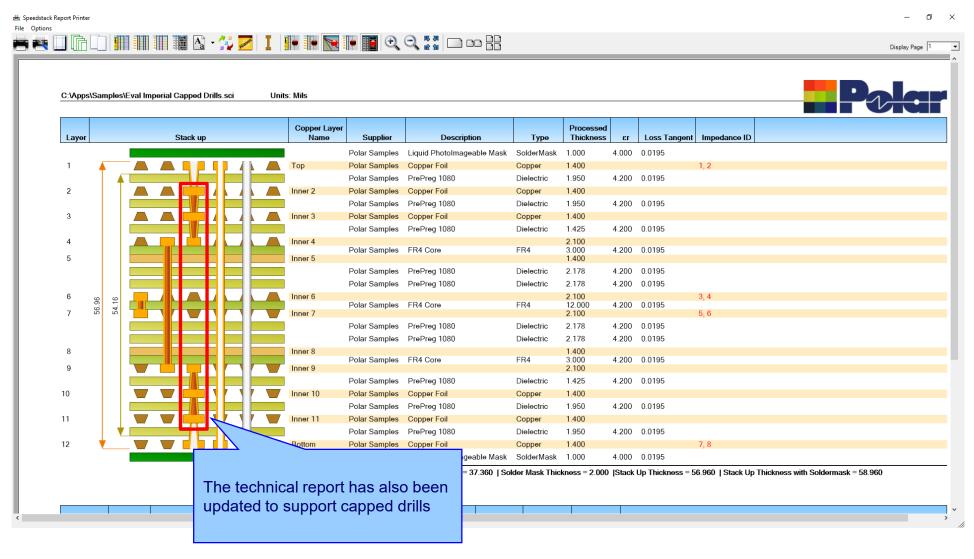

# New Drill Cap feature – technical report enhancements

### <u>Import / Export enhancements</u>

The following Import / Export options have been updated to support the drill cap properties introduced with Speedstack v21.07.08:

- XML STKX v22.00 and SSX v12.00 import / export options

- CSV export option

# Speedstack v21.05.06 (May 2021)

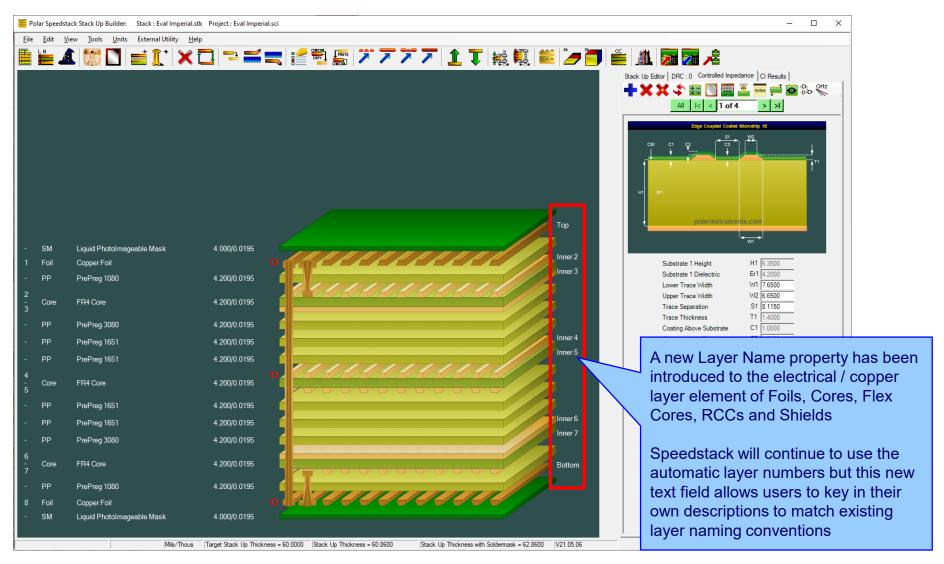

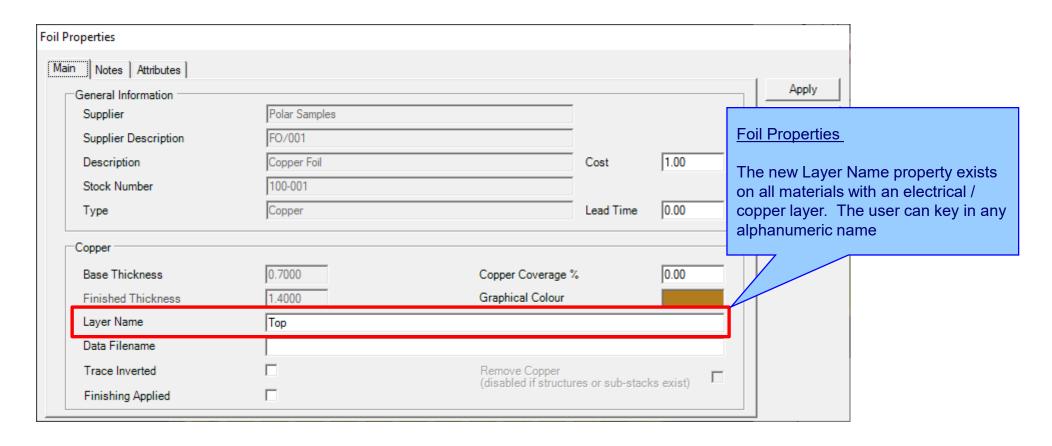

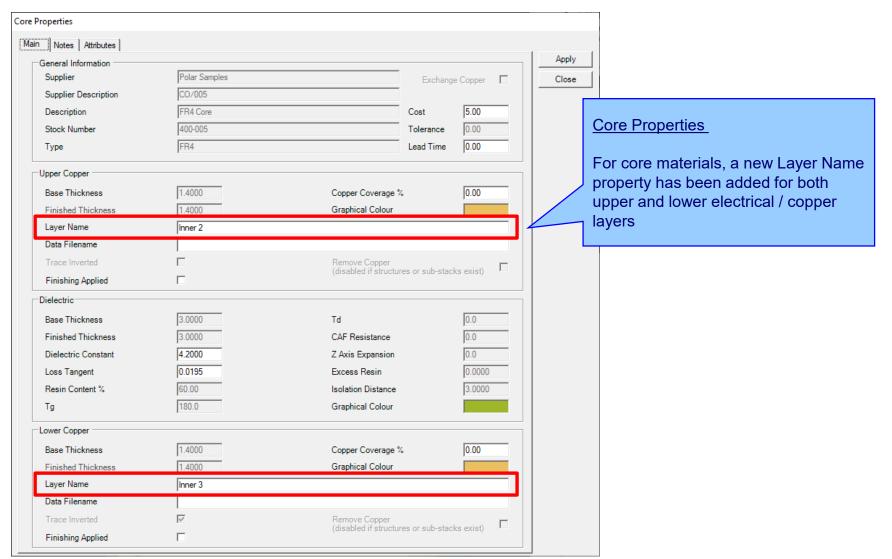

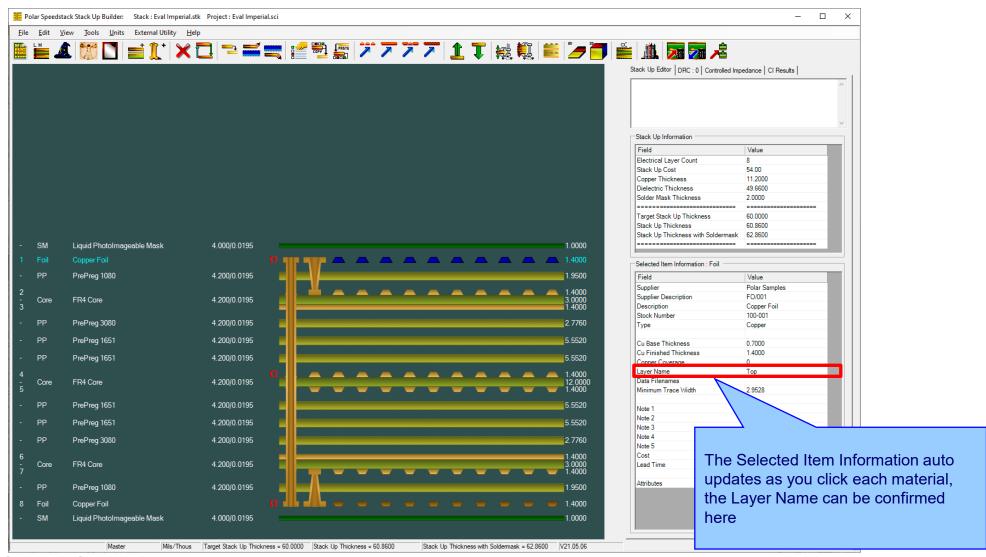

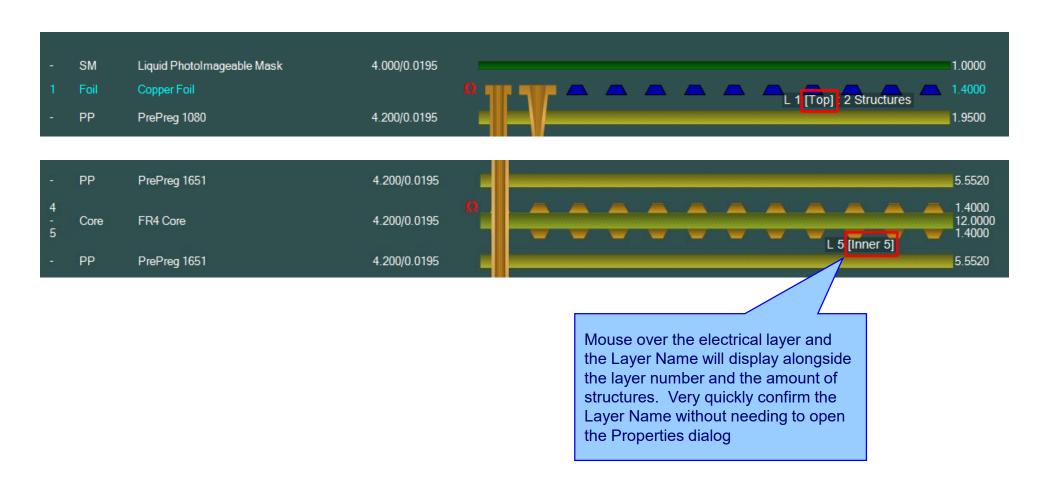

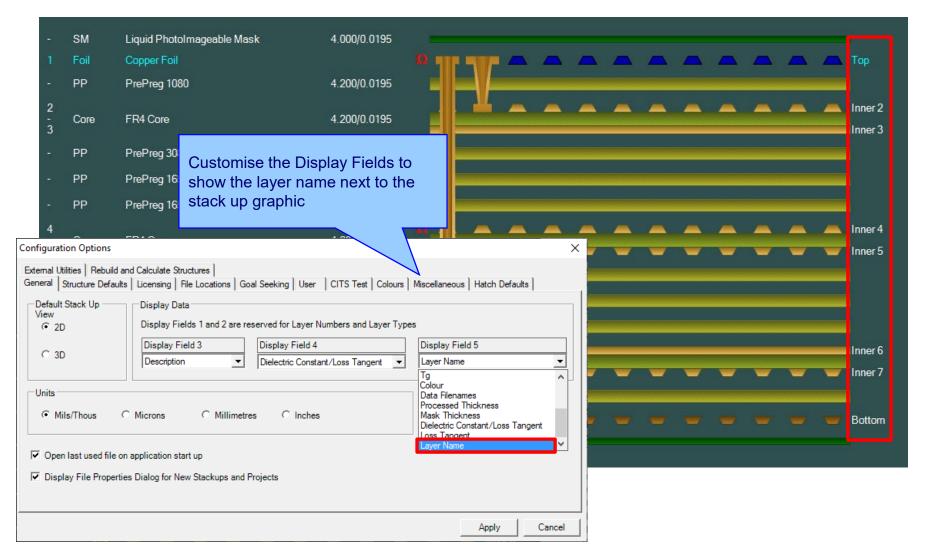

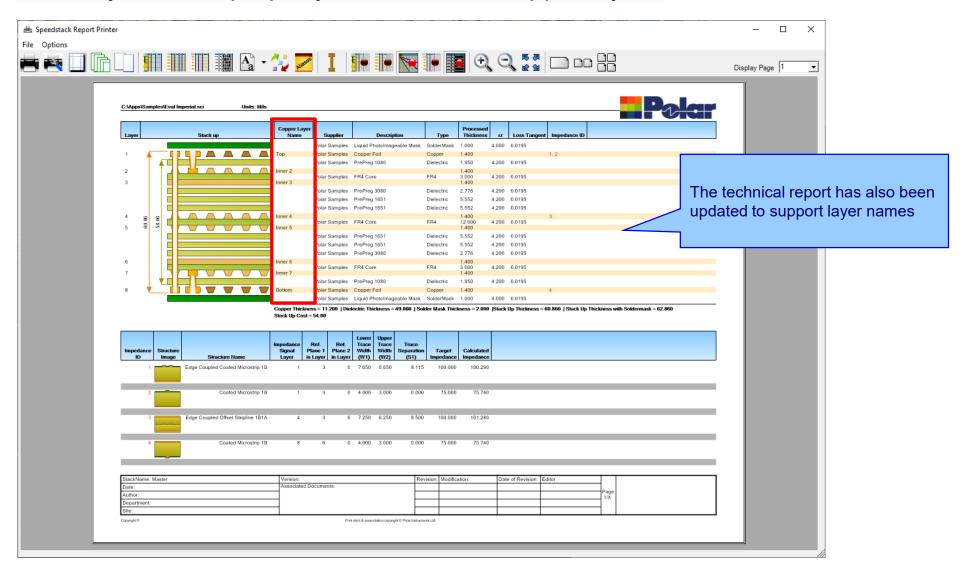

# New Layer Name property for electrical / copper layers

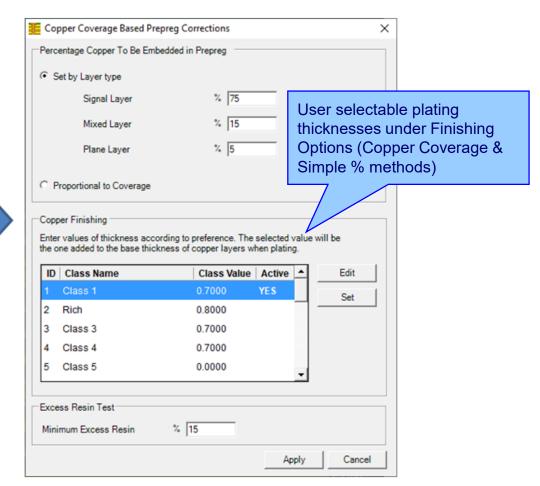

#### Copper Finishing classes increased

Speedstack v21.04 and earlier supported 4 classes

Speedstack v21.05 now supports 20 classes

#### <u>Import / Export enhancements</u>

The following Import / Export options have been updated to support the layer name property introduced with Speedstack v21.05.06:

- XML STKX v21.00 and SSX v11.00 import / export options

- CSV export option

- Gerber / DXF export option

# Speedstack v21.04.00 (April 2021)

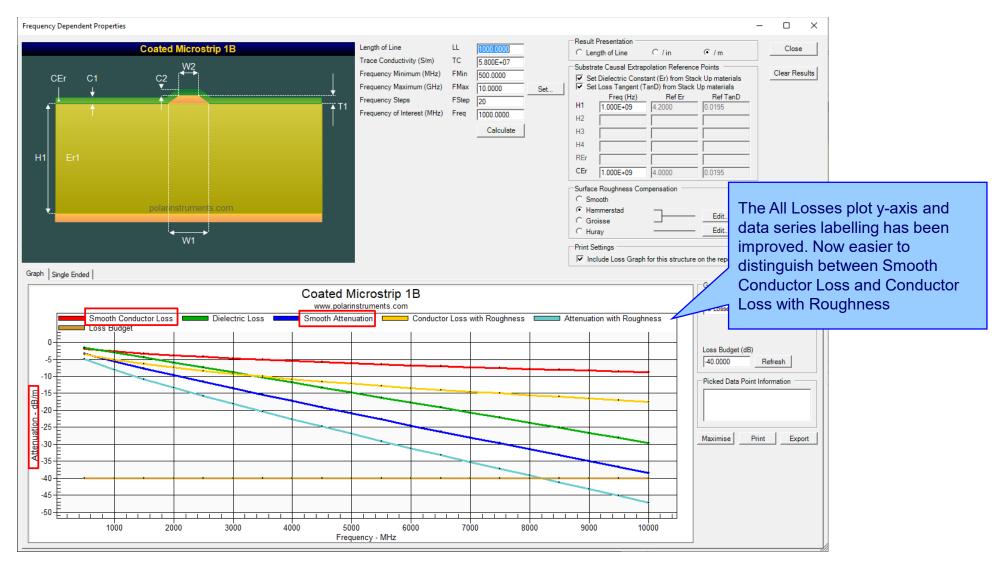

#### All Losses plot - clearer labelling

#### Other enhancements

- The controlled impedance and insertion loss Calculation Engine updated to the latest edition

- Frequency Dependent Calculations graphing library enhancements

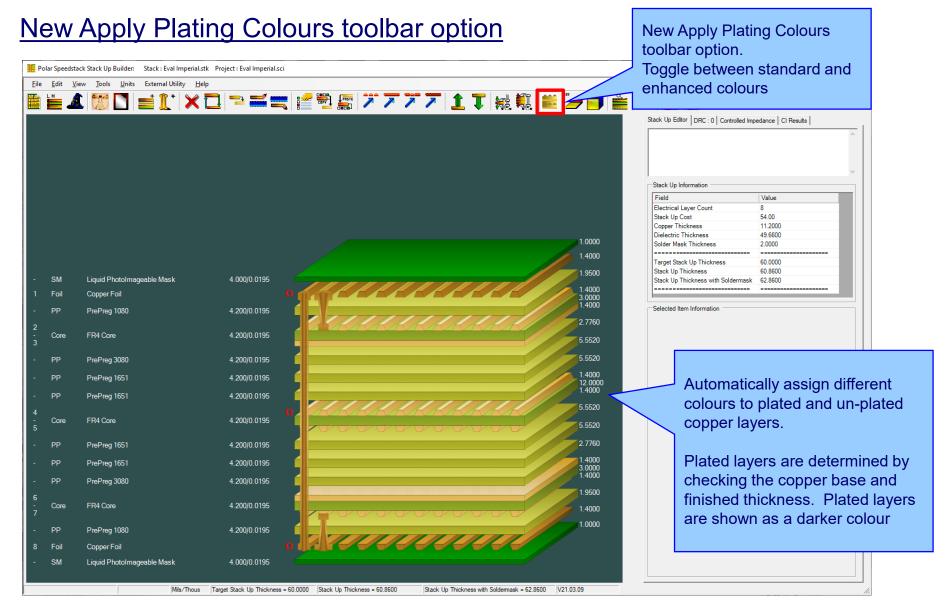

# Speedstack v21.03.09 (March 2021)

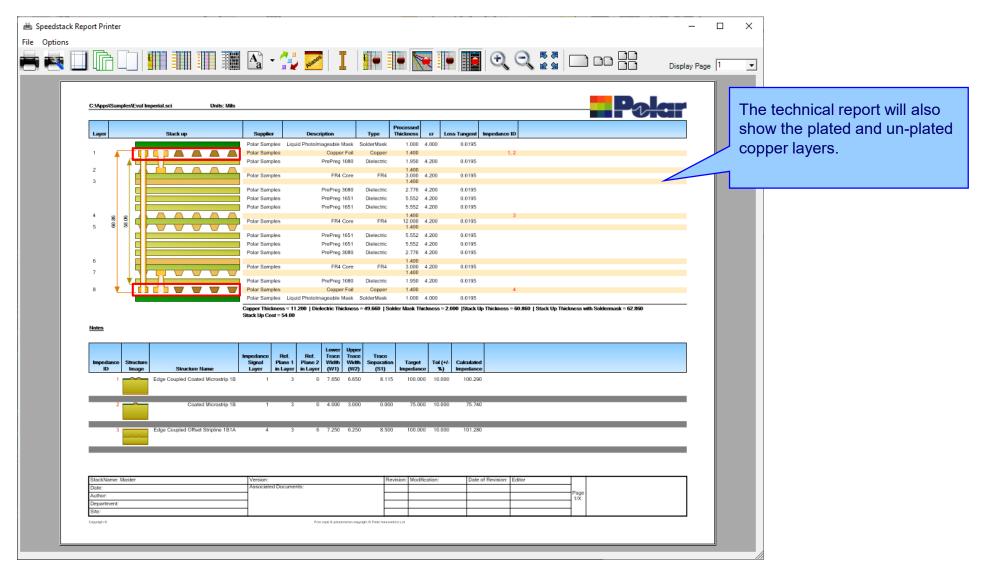

#### **Plated Copper Layers**

During PCB fabrication drill holes commonly have copper applied to the barrel wall by an electroplating process. This provides an interconnect between copper layers in the stack up.

This electroplating process often results in additional copper also being applied to the exposed copper layers where the mechanical drill starts / ends.

It is important to account for this additional plated copper thickness when calculating the overall stack up thickness and controlled impedance / insertion loss structures.

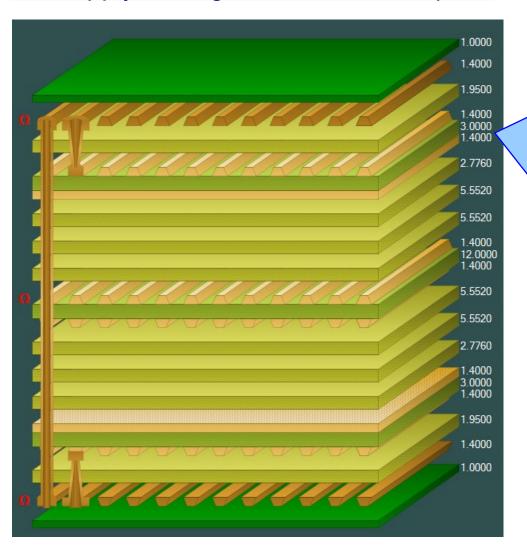

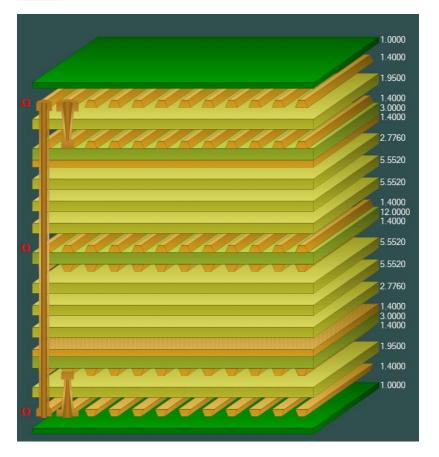

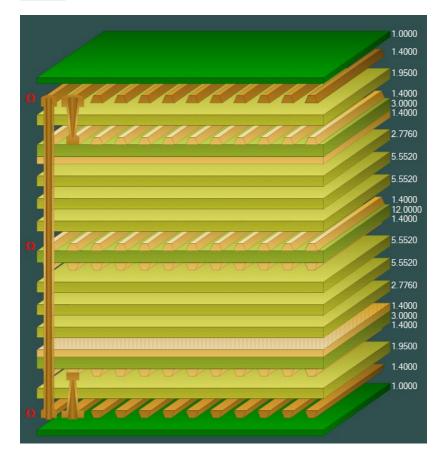

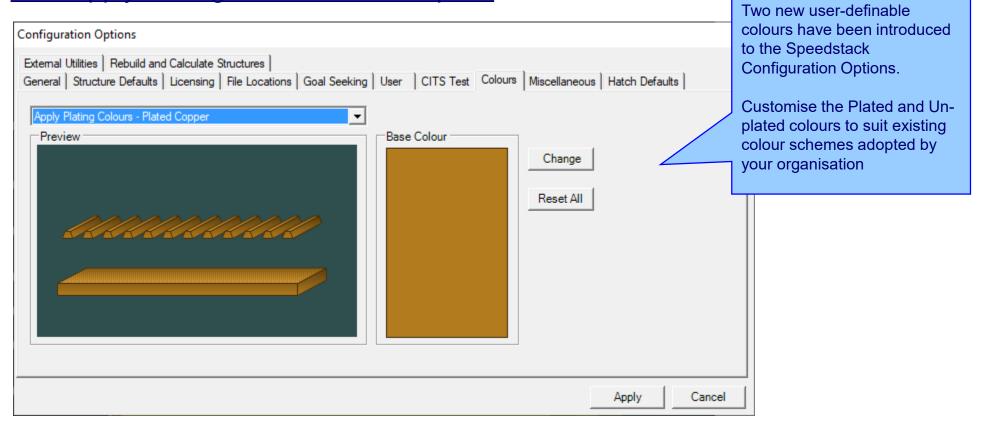

Speedstack has always allowed this additional plating thickness to be applied to the relevant copper layers. With v21.03 this has been enhanced further with automatic colour assignments to the plated and unplated layers

#### **Standard Colours**

## **Apply Plating Colours**

#### Online Library enhancements

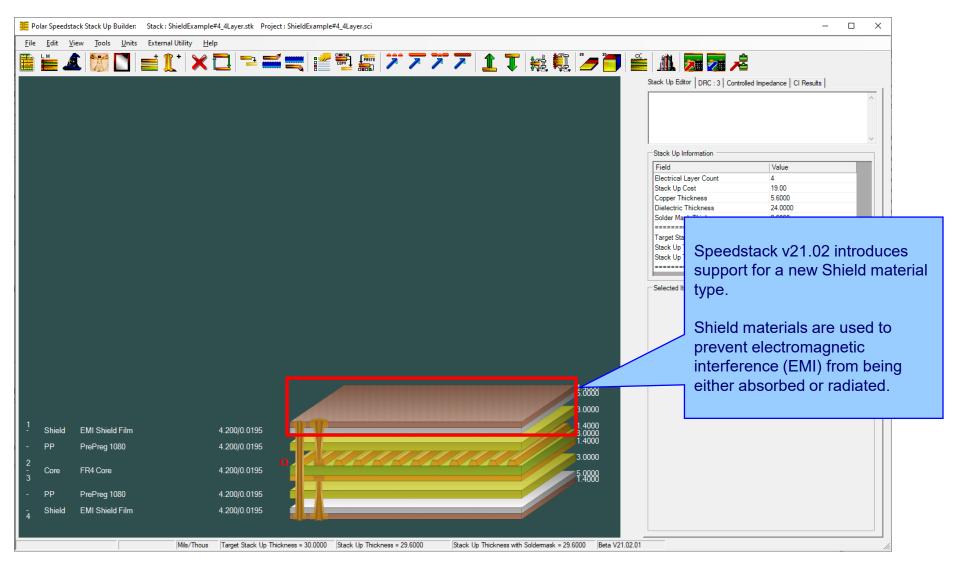

# Speedstack v21.02.01 (February 2021)

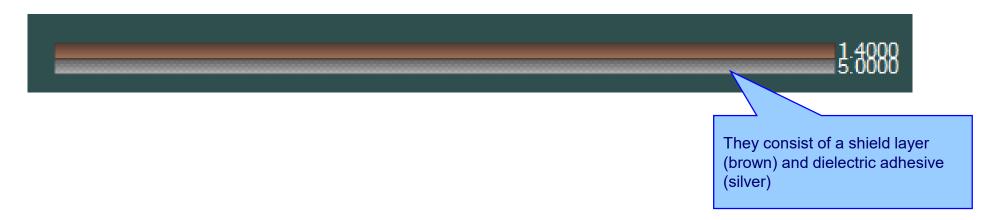

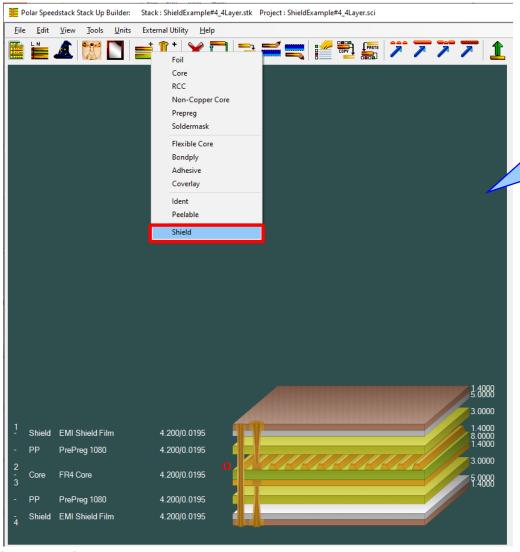

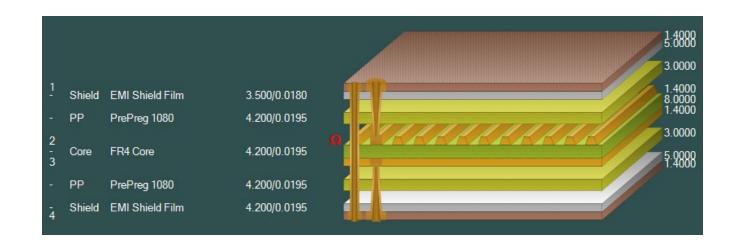

#### New Shield material

#### New Shield material Shields are typically applied to the outer layer(s) of the stack up 1.4000 5.0000 EMI Shield Film Shield 4.200/0.0195 PP PrePreg 1080 4.200/0.0195 3.0000 1.4000 8.0000 1.4000 FR4 Core 4.200/0.0195 Core PrePreg 1080 PP 4.200/0.0195 3.0000 4.200/0.0195 5.9888 1.4888 EMI Shield Film Shield

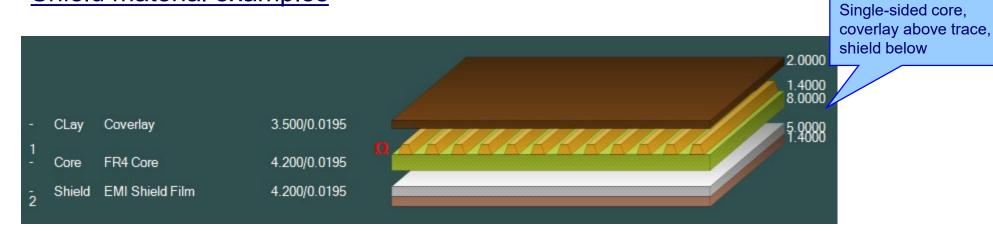

Example #1

## **Shield material examples**

1 Shield EMI Shield Film 4.200/0.0195

- Adh Adhesive 2 3.900/0.0195

2 Core FR4 Core 4.200/0.0195

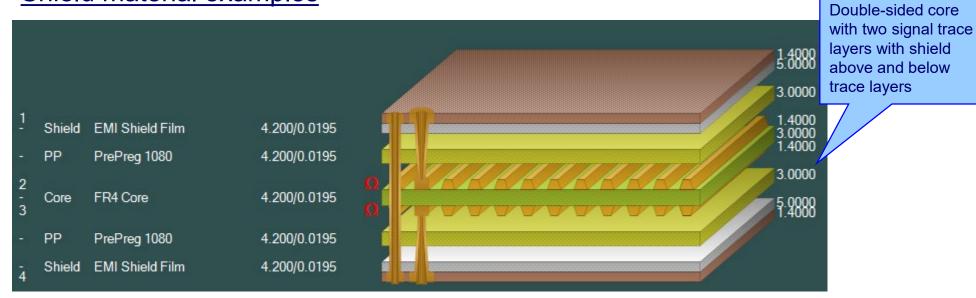

Example #2

Double-sided core, adhesive and shield above

Example #3

### Shield material examples

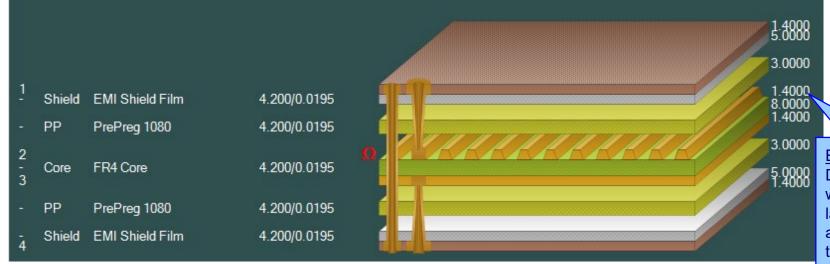

#### Example #4

Double-sided core with one signal trace layer with shield above and below trace layers

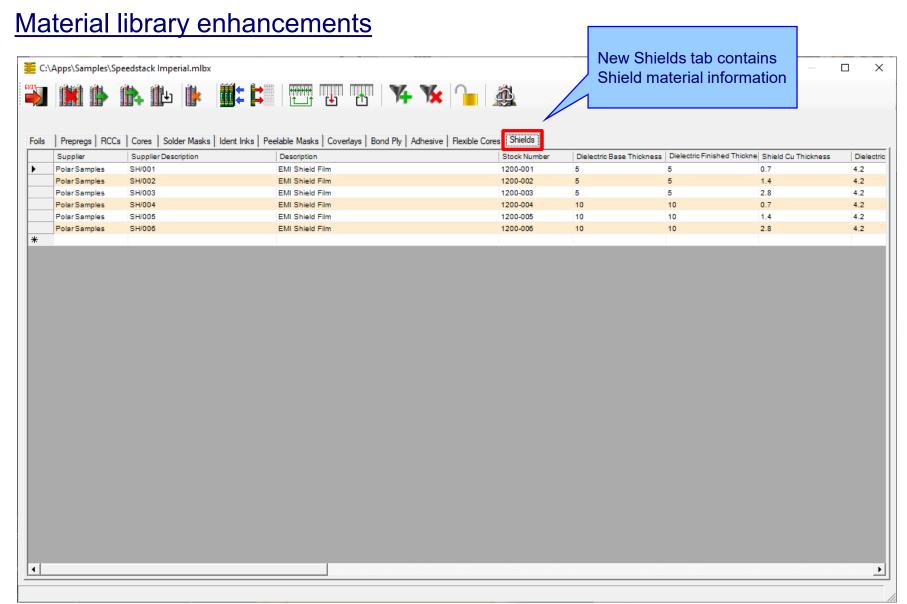

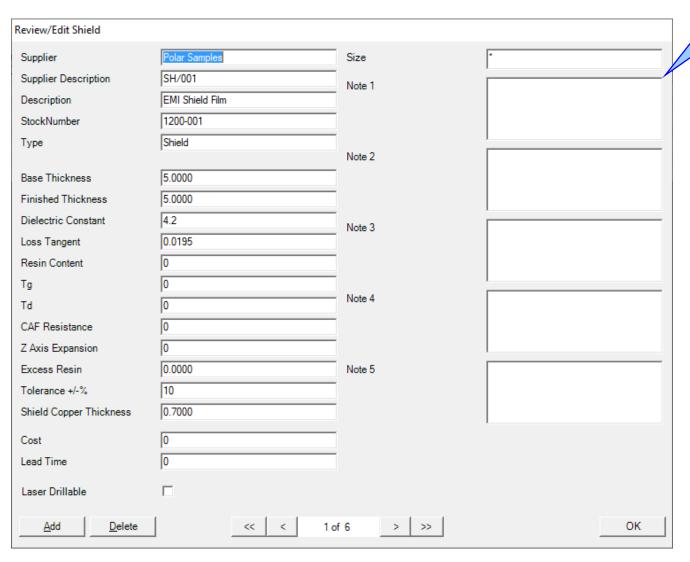

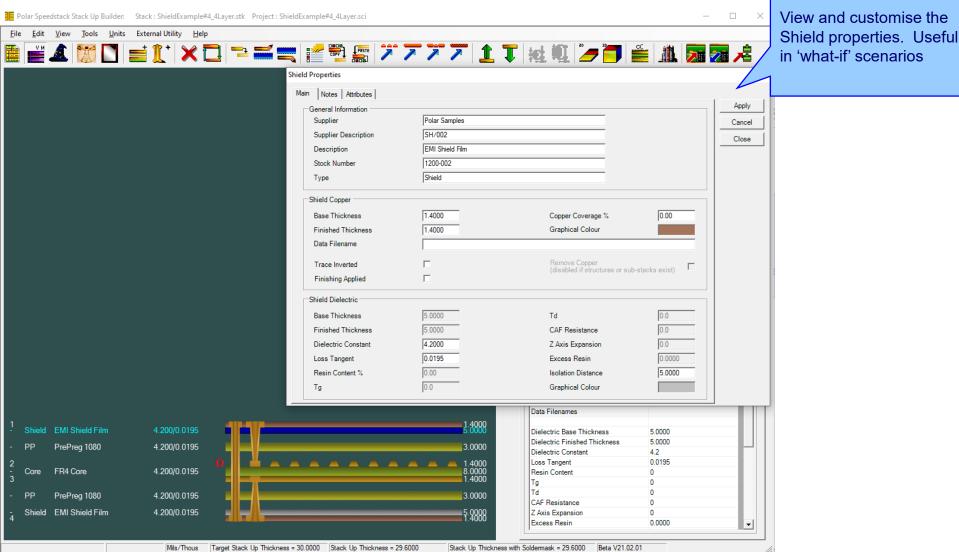

### Material library enhancements

Material library Edit Shield dialog

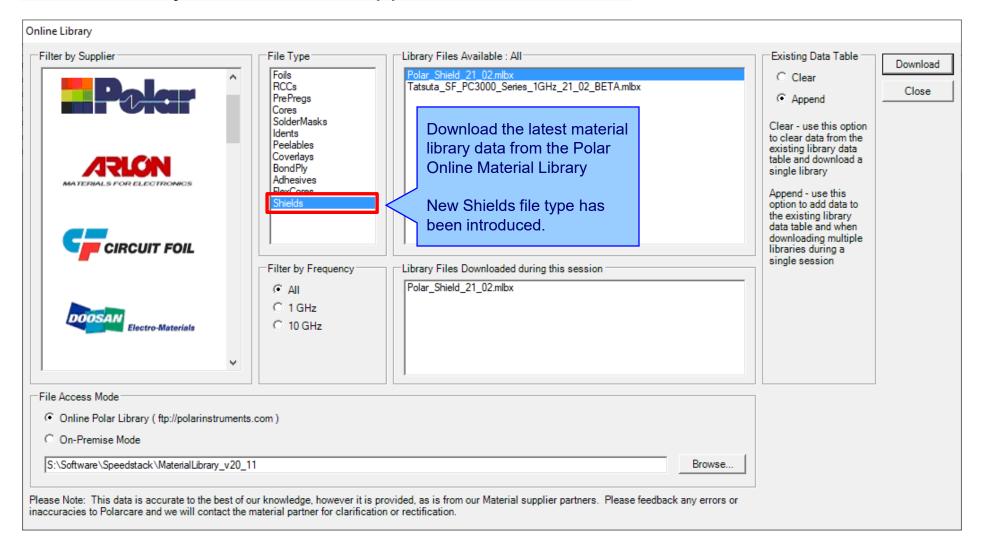

#### Online Library enhanced to support Shield materials

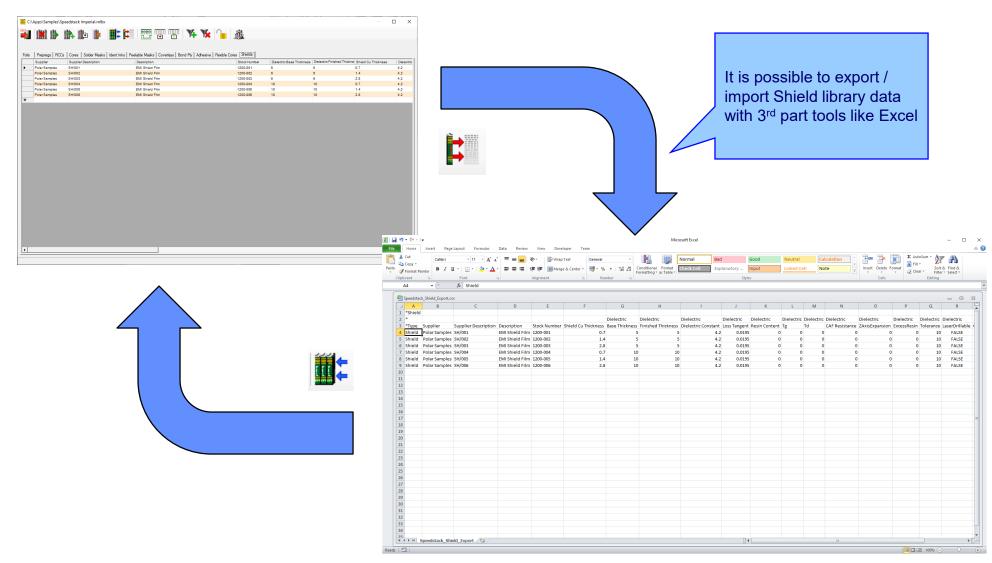

#### **Export / Import Shield library to Excel**

#### Stack up editor enhancements

Stack Up editor enhancements:

Shield material options to add, delete, swap, move up, move down, symmetry and set properties

# Shield properties Polar Speedstack Stack Up Builder: Stack: ShieldExample#4\_4Layer.stk Project: ShieldExample#4\_4Layer.sci - × File Edit View Tools Units External Utility Help

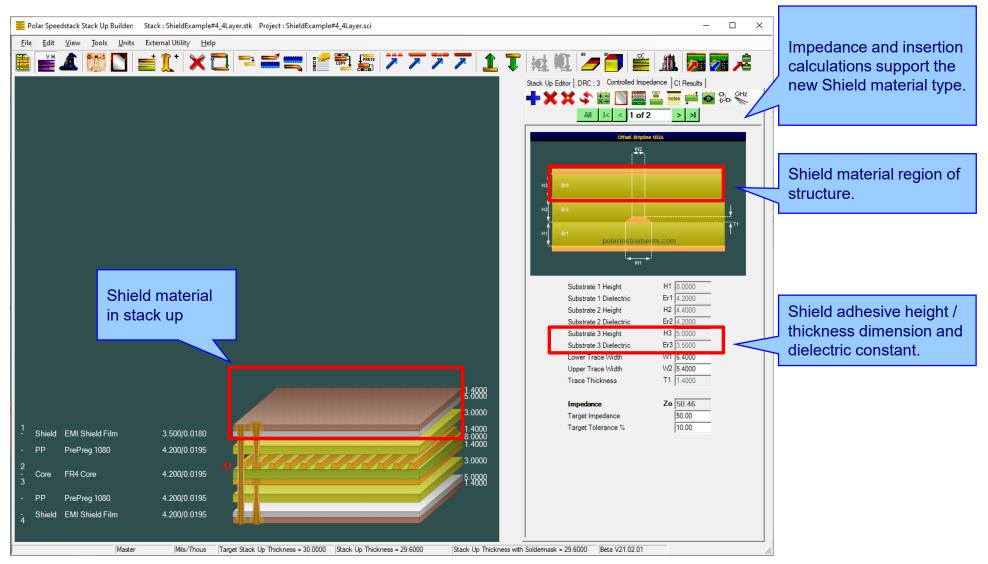

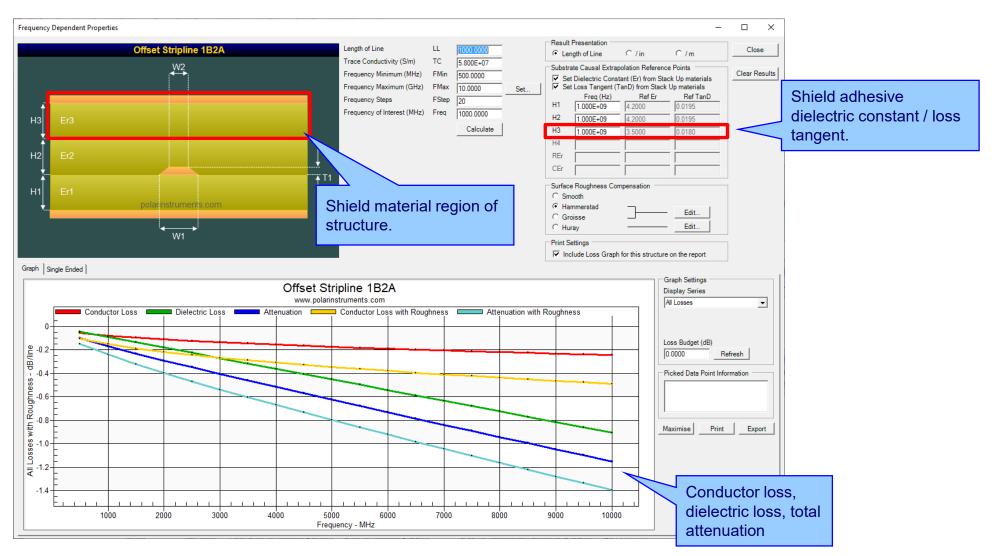

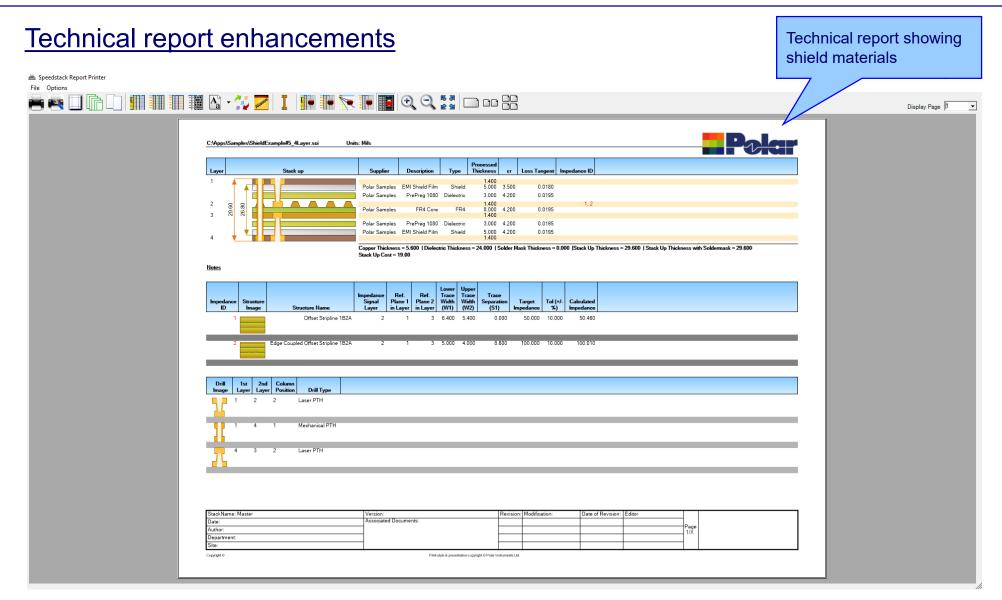

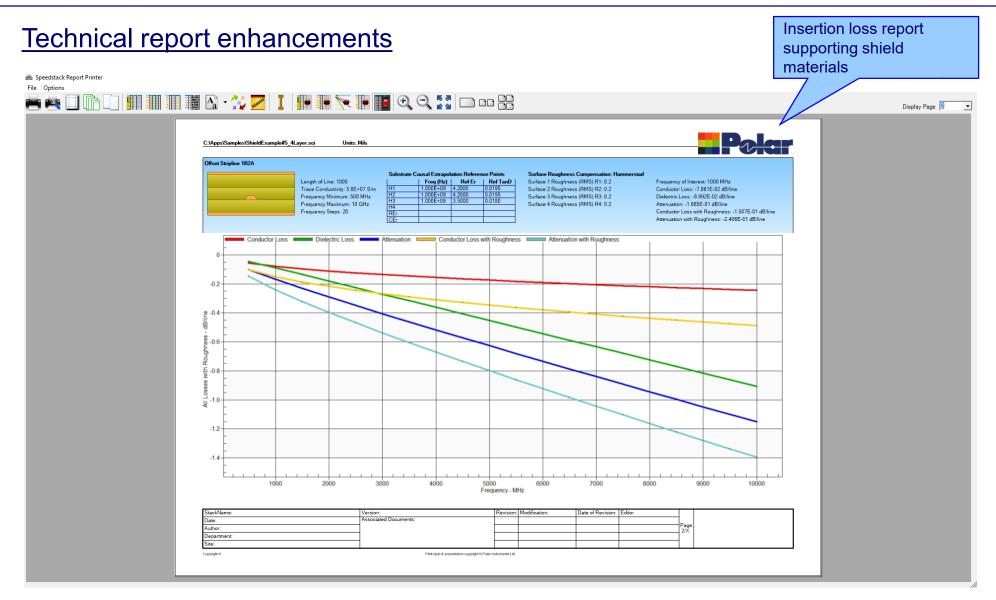

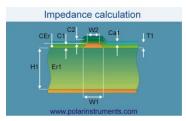

#### Controlled impedance and insertion loss calculations

#### Controlled impedance and insertion loss calculations

#### Controlled impedance and insertion loss calculations

Please note: Speedstack is capable of supporting many shield types for stack up design and documentation. However, it is important to use the correct type of shield material for controlled impedance and insertion loss applications. They are often designated by the shield vendor as 'for high speed signal transmission applications'.

#### <u>Import / Export enhancements</u>

The following Import / Export options have been updated to support the new shield material introduced with Speedstack 2021:

- XML STKX v20.00 and SSX v10.00 import / export options

- CSV export option

- Gerber / DXF export option

Thank you for viewing this Speedstack 2021 - 2023 preview. If you have questions we would be delighted to help you. Your local contact information is contained on the following slide

Polar Logo & graphic devices are registered trade marks of Polar Instruments Ltd.

Copyright Polar Instruments Ltd (c) 2023

For more information:

Contact Polar now: Phone

**USA / Canada / Mexico**

**Erik Bateham** (503) 356 5270

Asia / Pacific

Terence Chew +65 6873 7470

**UK / Europe**

**Neil Chamberlain** +44 23 9226 9113

Germany / Austria / Switzerland Hermann Reischer

+43 7666 20041-0

www.polarinstruments.com

Polar Logo & graphic devices are registered trade marks of Polar Instruments Ltd.

Copyright Polar Instruments Ltd (c) 2023