Überstehen Ihre Leiterplatten unbeschadet den Bleifrei-Lötprozess?

Applikationsschrift AP304

Die Bewährungsprobe für Ihre Leiterplatten

Die Einführung von Bleifrei-Lötprozessen bedeutet eine große Herausforderung für die Elektronikfertigung. Bei der Untersuchung der Leiterplatten-Zuverlässigkeit sollte man sich bewusst sein, dass der Bestück- und Lötprozess die größte Belastung für die Leiterplatte im gesamten Produktlebenszyklus darstellt:

|

|

Warum ist Bleifrei solch ein harter Test?

In den letzten Jahrzehnten hat sich der Fertigungsprozess ständig weiterentwickelt. Leiterplatten werden während der Fertigung nun häufiger und für längere Zeiten thermischen Belastungen ausgesetzt.

1. Betrachten wir eine einfache handgelötete Leiterplatte in konventioneller Durchsteck-Technik. Mit einer herkömmlichen Zinn-Blei-Legierung wird jede Lötstelle mit dem Lötkolben für wenige Sekunden auf ca. 200°C erhitzt.

2. In einer Wellenlötanlage wird das Board für ca. 1-2 Sekunden auf über 200°C erhitzt. Zuvor durchläuft die Leiterplatte eine Vorheizung, um das Flussmittel zu aktivieren.

3. Bei der einseitigen SMD-Bestückung wird der Lötprozess durch eine Doppelwelle ergänzt.

4.Für eine doppelseitige SMD-Bestückung wird ein Reflow-Prozess mit dem damit verbundenen Heiz- und Kühlzyklus eingesetzt.

5. Kommt eine BGA-Bestückung hinzu, so lässt sich eine weitere thermische Belastung durch gelegentliche Nachbearbeitung nicht vermeiden.

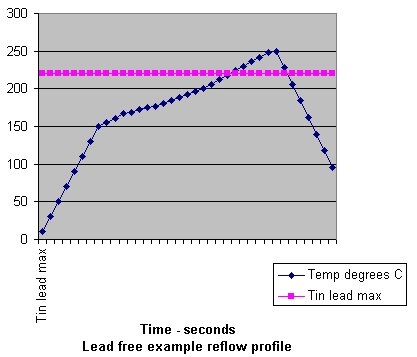

6. Mit Bleifrei-Prozessen werden nun all die oben angeführten Schritte bei einer deutlich erhöhten Temperatur von 245°C - 260°C durchgeführt. Die für zufrieden stellende Lötergebnisse erforderlichen Lötzeiten können umfangreiche und irreparable Schäden an Durchkontaktierungen und Innenlagenanbindungen verursachen. Um sicherzustellen, dass die Leiterplatten diese harten Belastungen überstehen, müssen die Leiterplattenmaterialien, das Design und die Fertigungsprozesse entsprechend abgestimmt werden.

Diese neuen Bedingungen in

Kombination mit kleineren Bohrdurchmessern und feineren Leiterbahnen

erfordern genaue Kenntnisse über das Verhalten der Leiterplatte und - am

wichtigsten - ob die Leiterplatte diese Frühphase des

Produktlebenszyklus übersteht.

Simulation des Fertigungsprofils:

Setzt man Testcoupons mit

einer Nachbildung der typischen Durchkontaktierungs-technologie (DK,

µvia, Stacked Via etc.) einem Temperaturprofil ähnlich dem

Bleifrei-Lötprozess aus, erreicht man eine entsprechende

Vorkonditionierung für den Langzeit-Zuverlässigkeitstest.

Der Durchlauf der Coupons durch eine Fertigungssimulation ergibt eine

wesentlich realistischere Vorbereitung für den beschleunigten

Zuverlässigkeitstest als dies mit normalen thermischen Profilen möglich

ist.

Die Fertigungssimulation auch für unkritische Boards.

Selbst Leiterplatten, welche in unkritischen Bereichen eingesetzt werden - wie z.B. Konsumelektronik - können einer Fertigungssimulation unterzogen werden, um zu prüfen, ob der Fertigungs- und Reworkprozess Schäden auf der Leiterplatte verursacht.

Wie kann das thermische Profil des Lötprozesses simuliert werden?

Der Interconnect Stress

Test (IST) ist eine bewährte Methode zur Simulation des

Fertigungsprozesses. Für IST wird ein Testcoupon in das

Leiterplattenpanel integriert. Der Coupon ist so konstruiert, dass

dieser ein statistisch gültiges Testvehikel für die Leiterplatte

darstellt. So wird z.B. der kleinste Bohrdurchmesser der Leiterplatte in

einer statistisch relevanten Anzahl (typisch 600 - 800

Durchkontaktierungen) für den Test wiedergespiegelt. Der Coupon enthält

speziell konstruierte Leiterbahnen für den Heizkreis. Diese

Heizleitungen befinden sich nahe der Oberfläche des Coupons, um ein

möglichst realistisches Temperaturprofil ähnlich einem Reflowprozess zu

simulieren. Der Coupon wird dann der gewünschten Anzahl von

Temperaturzyklen zur Simulation des Reflow/Rework Thermoprofils

unterzogen.

Wie werden die Coupons getestet?

Da die Coupons sehr kleine Abmessungen aufweisen, wird der Test als

Prüfdienstleistung angeboten. Bei größeren Volumina ist die Installation

eines eigenen IST Systems die wirtschaftlichere Lösung. Während der

Einführungsphase ist jedoch der IST-Test als Dienstsleistung die

bevorzugte Methode.

Was sind die Vorteile des IST Tests?

Der IST-Test ist eine

bewährte Zuverlässigkeits-Prüfmethode nach

IPC

TM-650 Standards.

Die Testergebnisse liegen innerhalb eines Tages

vor - im Vergleich zu mehreren Wochen bei

konventionellen Temperaturwechseltests. Noch wichtiger hingegen ist,

dass der IST-Test die hohen Temperaturen des Bleifrei-Lötprozesses exakt

simuliert. Nach der Fertigungssimulation kann der IST Test z.B. 200

Temperaturzyklen in 2 Tagen durchführen. Studien haben gezeigt, dass der

IST-Test eine ausgezeichnete Korrelation mit konventionellen Methoden

aufweist. (Bezug

auf IPC TR485)

Wo erhält man

Testcoupondaten?

Ein umfangreicher Datensatz mit IST Coupondesigns steht

hier zum Download zur Verfügung. Die Datei ist ca. 10 MB groß

und enthält sämtliche Informationen, um die IST Coupons in Ihre Panele

zu integrieren.